Digital Comprehensive Summaries of Uppsala Dissertations from the Faculty of Science and Technology 1039

# Towards Solution Processed Electronic Circuits Using Carbon Nanotubes

**ZHIYING LIU**

ACTA UNIVERSITATIS UPSALIENSIS UPPSALA 2013

ISSN 1651-6214 ISBN 978-91-554-8657-0 urn:nbn:se:uu:diva-198280 Dissertation presented at Uppsala University to be publicly examined in Häggsalen, Ångström Laboratory, Lägerhyddsvägen 1, Uppsala, Thursday, May 30, 2013 at 13:15 for the degree of Doctor of Philosophy. The examination will be conducted in English.

#### Abstract

Liu, Z. 2013. Towards Solution Processed Electronic Circuits Using Carbon Nanotubes. Acta Universitatis Upsaliensis. *Digital Comprehensive Summaries of Uppsala Dissertations from the Faculty of Science and Technology* 1039. 62 pp. Uppsala. ISBN 978-91-554-8657-0.

Emerging macro- and flexible electronic applications such as foldable displays, artificial skins, and smart textiles grow rapidly into the market. Solution-processed thin-film transistors (TFTs) based on single-walled carbon nanotubes (SWCNTs) as the semiconductor channel can offer high performance, low cost and versatility for macro- and flexible electronics. Major challenges to the development of SWCNT-based TFTs include: (i) hysteresis in their transfer characteristics (TCs), (ii) difficulties in simultaneous achievements of high on-state current  $I_{on}$  and large on/off current ratio  $I_{on}/I_{off}$ , and (iii) poor uniformity and scalability resulting from the poor solution processability. This thesis aims at developing reliable and simple process techniques for fabrication of the SWCNT-based TFTs that possess the afore-stated characteristics. It presents a systematic investigation to not only explore the fundamental device physics, but also develop novel fabrication methods for enhancement of device performance.

First, issues related to the measurement of gate capacitance ( $C_{\rm g}$ ), the determination of current scalability, and the hysteresis in randomly networked SWCNTs are properly addressed. This leads to the establishment of a comprehensive methodology for extraction of carrier mobility ( $\mu$ ) for the SWCNT-based TFTs. In detail, the large hysteresis is effectively suppressed by adopting a pulsed drain current-gate voltage ( $I_{\rm d}$ - $V_{\rm g}$ ) method in which the polarity of the gate pulse was alternating during the measurement. Different from most reported methods in the literature,  $C_{\rm g}$  is accurately determined in our case by performing direct capacitance-voltage measurement on the TFTs.

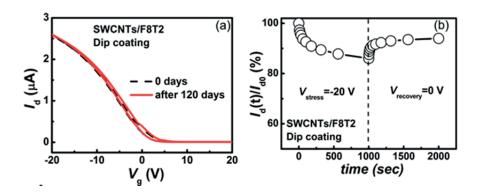

Second, with the employment of functional composites comprising SWCNTs embedded in a semiconducting polymer, poly-9,9 dioctyl-fluorene-cobithiophene (F8T2), as the semiconducting channel via facile solution processes under ambient conditions, the fabricated TFTs exhibit outstanding electrical performance with: (i) negligible hysteresis, (ii) high  $\mu$ , (iii) high  $I_{on}$  and large  $I_{on}/I_{off}$ , (iv) excellent uniformity and dimensional scalability, and (v) good stability. These highly desired performance parameters are achieved owing to an ideal composite structure with metallic SWCNTs being selectively removed and the remaining semiconducting SWCNTs being well wrapped by the polymer matrix.

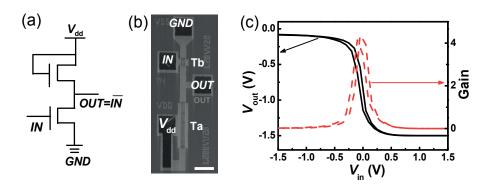

Finally, the developed TFTs basing on the SWCNT/F8T2 composite are used as the building block to construct some logic circuits. The resultant inverters, NANDs, and NORs are found to retain the small-hysteresis characteristics, with a cut-off frequency reaching 100 kHz. The results presented in this thesis advance the state-of-art SWCNT-based macroelectronics.

Zhiying Liu, Uppsala University, Department of Engineering Sciences, Solid State Electronics, Box 534, SE-751 21 Uppsala, Sweden.

© Zhiving Liu 2013

ISSN 1651-6214 ISBN 978-91-554-8657-0

urn:nbn:se:uu:diva-198280 (http://urn.kb.se/resolve?urn=urn:nbn:se:uu:diva-198280)

Dedication to my family

# List of Papers

This thesis is based on the following papers, which are referred to in the text by their Roman numerals.

- I. On Gate Capacitance of Nanotube Network

<u>Z Liu</u>, J Li, Z-J Qiu, Z-B Zhang, L-R Zheng, S-L Zhang, IEEE Elec.

Dev. Lett, vol. 32, no. 5, pp. 641-643, 2011.

- II. Mobility Extraction for Nanotube TFTs

Z Liu, Z-J Qiu, Z-B Zhang, L-R Zheng, S-L Zhang, IEEE Elec. Dev. Lett, vol. 32, no. 7, pp. 913-915, 2011.

- III. Solution-Processable Nanotube/Polymer Composite for High-Performance TFTs

Z Liu, Z-B Zhang, Q Chen, L-R Zheng, S-L Zhang, IEEE Elec. Dev. Lett, vol. 32, no. 8, pp. 1299-1301, 2011.

- IV. Small-Hysteresis Thin-Film Transistors Achieved by Facile Dipcoating of Nanotube/Polymer Composite

Z Liu, H Li, Z-J Qiu, S-L Zhang, Z-B Zhang, Adv. Mater, vol. 24, pp. 3633-3638, 2012.

- V. Solution-Processed Logic Gates Based On Nanotube/Polymer Composite

Z Liu, X Gao, Z Zhu, Z Qiu, D Wu, Z-B Zhang, S-L Zhang, Revised submission to IEEE Trans. Electron Device, 2013.

## **Related Publications**

I. Thin-Film Field-Effect Transistors Based on Composites of Semiconducting Polymer and Carbon Nanotubes

Z Liu, Z-B Zhang, M Qu, J Li, A Cabezas, L-R Zheng, S-L Zhang, Oral presentation at the 217th Electrochemical Society (ECS) Meeting, Vancouver, Canada, Apr. 25-30, 2010.

II. Hysteresis-Free Thin-Film Transistors Achieved by Novel Solution-Processing of Nanotube/Polymer Composite

Z Liu, H Li, Z-J Qiu, L-R Zheng, S-L Zhang, Z-B Zhang, Poster at

<u>Z Liu</u>, H Li, Z-J Qiu, L-R Zheng, S-L Zhang, Z-B Zhang, Poster at the Material Research Society (MRS) meeting, San Francisco, USA, Apr 09-13,2012.

III. Ink-jet printed thin-film transistors with carbon nanotube channels shaped in long strips

J Li, T Onander, A López Cabezas, B Shao, <u>Z Liu</u>, Z-B Zhang, I Jõgi, X Gao, M Boman, L-R Zheng, M Östling, H-E Nilsson, S-L Zhang, J Appl Phys, vol. 109, no. 8, 084915, 2011.

VI. Inkjet printing of stripe-featured single-walled carbon nanotube thin film transistors

J Li, M Qu, <u>Z Liu</u>, A López Cabezas, B Shao, T Unander, Z-J Qiu, Z-B Zhang, J Zhou, Y Huang, L-R Zheng, H-Erik Nilsson, S-L Zhang, Oral presentation in Materials Research Society (MRS) Fall Meeting, Dec. 2, 2009, Boston.

Reprints were made with permission from the respective publishers.

# Symbols & Acronyms

C Total capacitance of the nanotube network

$E_{\rm g}$  Bandgap

$f_{\rm c}$  Characteristic frequency  $f_{\rm m}$  Measurement frequency

$f_{\rm T}$  Cut-off frequency  $g_{\rm m}$  Transconductance  $I_{\rm d}$  Drain current

$I_{\text{dsat}}$  Drain current in saturation region

$I_{\rm on} (I_{\rm off})$ On (off) -state current On/Off current ratio  $I_{\rm on}/I_{\rm off}$ Propagation constant k LChannel length Nanotube length  $L_{\rm nt}$ Current exponent m Surface coverage p Percolation threshold  $p_{\rm c}$

R Total resistance of the nanotube network

$R_{\rm c}$  Contact resistance  $t_{\rm off}(t_{\rm on})$  Pulse off (on) period  $t_{\rm ox}$  Gate oxide thickness

$\begin{array}{ccc} V_{\rm g} & & {\rm Gate\ potential} \\ V_{\rm g}^{\rm max} & & {\rm Measurement\ range} \\ V_{\rm t} & & {\rm Threshold\ voltage} \\ V_{\rm in} & & {\rm Input\ voltage} \\ V_{\rm out} & & {\rm Output\ voltage} \\ V_{\rm dd} & & {\rm Supply\ voltage} \\ W & & {\rm Channel\ width} \end{array}$

$Z_0$  Characteristic impedance of the nanotube network

$egin{array}{lll} lpha & & & & & & \\ \mu & & & & & & \\ \mathcal{E}_0 & & & & & & \\ \end{array}$

$\varepsilon_{\text{ox}}$  Relative permittivity of gate oxide

$\rho$  Nanotube density

$\rho_{\rm c}$  Critical nanotube density

wAngular frequency $\Delta V_{\rm H}$ Hysteresis gap1-DOne-dimensional2-DTwo-dimensional

AFM Atomic force microscopy

ALD Atomic layer deposition

AP Alternating polarities

APTS 3-aminopropyltriethoxysilane

a-Si Amorphous-Si CNT Carbon nanotube

CP Conventional pulsed method

*C-V* Capacitance-voltage

D Drain

DGU Density gradient ultracentrifugation

DS Drop spacing

EBE Electron-beam evaporation

F8T2 Poly(9,9-dioctylfluorene-co-bithiophene)

HMDS Hexamethyldisilazane

IGZO InGaZnO

MIS Metal-insulator-semiconductor

m-SWCNT Metallic single-walled carbon nanotube

OTS Octadecyltrichlorosilana P3AT Poly(3-alkylthiophene)s

PFO Poly(9,9-dioctylfluorenyl-2,7-diyl)

PMMA Poly(methyl methacrylate)

RBM Radial breathing mode

RT Room temperature

S Source

SAM Self assembly monolayer

SDBS Sodium dodecylbenzene sulphonate SWCNT Single-walled carbon nanotube

s-SWCNT Semiconducting single-walled carbon nanotube Si-MOSFET Si metal-oxide-semiconductor field effect transistor

Si≡OH SiO<sub>2</sub> surface-bonded water molecule

TC Transfer characteristic

TFT Thin film transistor

TL Transmission line

TMA Trimethylaluminum

## Acknowledgements

I would like to express my deep gratitude to my main supervisor, Prof. Shi-Li Zhang, for his mentorship, encouragement and guidance during the whole Ph.D period. The experience of working as his student not only teaches me the approaches for scientific research, but also the attitude toward life. His contribution to this thesis is more than what I can express by words. I also would like to thank my co-supervisor, Prof. Li-Rong Zheng, for his inspirational discussion, continuous encouragement and enormous support. He demonstrates to me how a researcher should be passionate, confident and open-minded in his life.

Deep gratitude is given to Doc. Zhi-Bin Zhang, my practical supervisor, for teaching me the techniques in the laboratory as well as the extensive discussions in every research topic. I sincerely thank Dr. Zhi-Jun Qiu in Fudan university for his enormous efforts and constructive suggestions during the collaborations. I also would like to thank Dr. Qiang Chen in KTH, for his kind help, support, as well as the inspirational discussions.

It is a great pleasure to work with all the colleges at Emerging Electronics group in Uppsala University. They are Patrik Ahlberg, Dr. Zhiwei Zhu, Malkolm Hinnemo, Dr. Xindong Gao, Dr. Si Chen, Da Zhang, Man Song, Seung Hee Jeong and Seyed Reza Moossavi. Their kind help and insightful suggestions contribute a lot to this thesis.

Many thanks are given to all the colleges in the Division of Solid-State Electronics in Uppsala University, for creating such a conducive and creative research environment. Special acknowledgements are given to Prof. Jörgen Olsson and Dr. Örjan Vallin for carefully reviewing my thesis, Prof. Marika Edoff, Dr. Jonas Pettersson, Dr. Lars Vestling, Prof. Jörgen Olsson (again), Dr. Örjan Vallin (again), Ling-Guang Li, Sara Lotfi, Prof. Ilia Katardjiev, Milena De A. Moreira, and Doc. Hans Norström for their kind help as well as lab assistance, and Marianna Asplund for the excellent administrative work.

I am grateful to the colleges in Electrum Laboratory KTH, especially for their lab assistance and the happy time spent together. They are Dr. Yong-Bin Wang, Dr. Jiantong Li, Dr. Ana Lopez Cabezas, Dr. Gunnar Malm, Esteban Bernales Forsberg, Reza Sanatinia, Dr. Shagufta Naurenen, Dr. Abhilash Sugunan, Dr. Hans Bergqvist, Dr. Ying Ma, Dr. Xiaodi Wang, Dr. Abhilash Sugunan, Terrance Burks, Yichen Zhao, Dr. Min Yan, Fei Lou, Yiting Chen, Kunli Xiong, Xi Chen and Miao Zhang.

I also would like to thank all the members at iPACK center, KTH, especially Dr. Ana Lopez Cabezas (again), Yi Feng, Dr. Yasar Amin and Dr. Matti Mäntysalo for the joyful periods spent in office, and Awet Yemane Weldezion, Iris Jie Gao, Dr. Jian Chen, Geng Yang, Dr. Huimin She, Dr. Zhou Zou, Qiansu Wan, Jue Shen, Dr. Liang Rong, Li Xie, Shaoteng Liu and Ning Ma for their kind help.

A special acknowledgement goes to Prof. Ming-Fu Li and Prof. Daming Huang, my previous supervisors in Fudan University. The knowledge and approaches they thought me benefit not only this thesis, but also my whole academic career.

Finally, my deepest gratitude goes to all my family members, for their endless love, patience and support in my life. Specially, I would like to thank my husband, Botao Shao, for reviewing each of my manuscripts as well as this thesis, offering me valuable suggestions in each topic, and sharing the joys and sorrows these years.

> Zhiying Liu Apr. 2013 Uppsala

# Contents

| 1. Introduction                                             | 1  |

|-------------------------------------------------------------|----|

| 2. Fundamentals                                             |    |

| 2.1 Thin-film transistor (TFT) architectures                |    |

| 2.2 Percolation transport in nanotube networks              |    |

| 2.3 Electrical characteristics of SWCNT-network TFTs        |    |

| 2.4 Hysteresis in SWCNT-based TFTs                          | 12 |

| 3. Experimental Approaches                                  | 15 |

| 3.1 Dispersion of nanotubes in solution                     | 15 |

| 3.1.1 Surfactant aided solubilization                       | 15 |

| 3.1.2 Polymer aided solubilization                          | 15 |

| 3.2 TFT fabrication                                         |    |

| 3.2.1 Substrate preparation                                 | 16 |

| 3.2.2 Channel formation                                     | 17 |

| 3.3 Electrical characterizations.                           |    |

| 3.3.1 Hysteresis suppression by pulsed $I_d$ - $V_g$ method | 21 |

| 3.3.2 Gate capacitance $(C_g)$ of networked nanotubes       | 23 |

| 3.4 Mobility ( $\mu$ ) extraction                           |    |

| 3.4.1 Dependence of $\mu$ on hysteresis                     |    |

| 3.4.2 Dependence of $\mu$ on $C_{\rm g}$                    |    |

| 3.4.3 Dependence of $\mu$ on current scaling behavior       | 28 |

| 4. Carbon Nanotube TFTs and Circuits                        |    |

| 4.1 Development of solution processing technology           | 31 |

| 4.2 Hysteresis suppression                                  | 32 |

| 4.3 Switch performances                                     | 35 |

| 4.4 Uniformity and scalability                              | 36 |

| 4.5 Ambient and operational stabilities                     |    |

| 4.6 Logic circuits                                          | 38 |

| 5. Overview of the Appended Papers                          | 41 |

| 6. Summary and Outlook                                      | 45 |

| Sammanfattning på svenska                                   | 49 |

| References                                                  | 53 |

| Appendix A                                                  | 61 |

## 1. Introduction

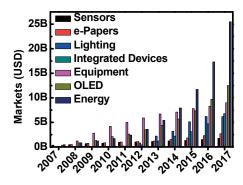

In parallel with the development of microelectronics technology with more transistors in a smaller area, a new branch of applications that require the electronics to spread over a large area, often referred to as macroelectronics [1], has emerged. The term of macroelectronics is related to flexible electronics since the products can be manufactured on flexible plastics, papers as well as textiles with extraordinary bendability or stretchability. The development of macro- and flexible electronics opens up a large variety of novel applications such as foldable displays [2], printed thin-film solar cells [3], artificial skins [4], solid-state lighting [5], etc, as shown in Fig. 1.1 [6]. Currently, such products grow exponentially to the market. It is estimated by FlexTech that by 2017, the market of macro- and flexible electronics products in total including photovoltaics, OLED, lighting, integrated displays, etc. will exceed \$60B annually [6].

For macro- and flexible electronics, mechanical flexibility, portability, and low fabrication cost, instead of high density of high-speed transistors, are the desirable properties. Take displays as an example, thin-film transistors (TFTs) with carrier mobility ( $\mu$ ) around 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and dimensions of the order of 10  $\mu$ m are sufficient [7]. Currently, the state-of-art thin films such as amorphous silicon (a-Si) and polycrystalline silicon (poly-Si) can well fulfill these requirements and have grown into a huge industry. However, large–area displays are still expensive due to the high manufacturing

Fig. 1.1 Predicted market growth of macro- and flexible electronics applications [6].

cost caused by the unavoidable sophisticated vacuum processes. Conventionally, Si based devices lack mechanical flexibility unless sophisticated layer transfer technique is utilized [8].

Motivated by their light-weight, flexibility, and multi-functionality, organic materials, such as semiconducting polymers, have attracted special attention. An added advantage with the organic materials is their relative ease in deposition on various substrates through low temperature solution processes [3,9]. The compatibility of organic materials with the newly developed printing techniques such as gravure printing, screen printing, and ink-jet printing on flexible substrates enables the high-throughput, ultra-low cost manufacture of flexible products [2,10,11]. However, those organic materials usually suffer from two shortcomings. One is the inferior  $\mu$  which is generally lower than that of a-Si. Although the low  $\mu$  value might still suffice for certain applications, enhancements in  $\mu$  would facilitate the exploration of a wider range of possibilities [1]. The other challenge is the poor electrical stability under bias stress or in the ambient air, which is represented by threshold voltage  $(V_t)$  shift and on-state current  $(I_{on})$  degradation [12,13]. These are severe effects since the devices may fail in operation. It is clear that a new class of materials is necessary to alleviate these restrictions.

Metal oxides, including single metal compounds (*e.g.*, In, Ga, Zn, and Sn) and alloys such as InGaO, ZnSnO, InZnO, and InGaZnO (IGZO) represent a special class of new and attractive TFT materials. Among them, IGZO is particularly interesting since it can offer  $\mu$  values ranging from 1 to 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, although it is amorphous rather than polycrystalline [14]. The processing temperature for amorphous IGZO can range from room temperature (RT) up to >300 °C. At RT,  $\mu$  remains higher than 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, which is of great potential for flexible electronic applications. However, these materials suffer from severe stability issue due to the generation of oxygen vacancies. Typically, they are also rigid mechanically, similar to a-Si films.

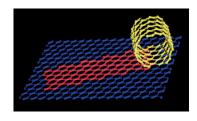

Concurrently, carbon nanotubes (CNTs), since the discovery by Iijima in 1991 [15], have gained enormous attention due to their unique structural, mechanical, and electrical properties. A single-walled carbon nanotube (SWCNT) can be viewed as a thin, long and hollow cylinder rolled from a graphene sheet along its circumferential direction, as shown in Fig. 1.2 [16]. The high aspect ratio (length-to-diameter, >10³) and the giant specific surface area (1600 m²/gram) are critical for chemical and biochemical sensing applications. Mechanically, CNTs possess a Young's modulus at ~1 TPa and a tensile strength about 150 GPa, demonstrating excellent flexibility and robustness. Owing to the molecular homogeneity and quasi one-dimensional (1-D) structure, SWCNTs are expected to exhibit near ballistic transport [17]. In 1998, the first transistor based on an individual SWCNT was fabricated and it was proven with extremely high intrinsic  $\mu$  (~3000 cm²V⁻¹s⁻¹) and high current-carrying capacity (7000  $\mu$ A/ $\mu$ m) [18]. Subsequent publications confirmed  $\mu$  of individual SWCNTs to be in the range of 10³-10⁵ cm²V⁻¹s⁻¹ [19,-

Fig. 1.2 Schematic illustration of an SWCNT rolled from a graphene sheet [16].

20], which exceeds that of most semiconductors and suggests the possibility of SWCNTs in high-speed electronics applications.

When synthesized in a usual way, SWCNTs can be either metallic (m) or semiconducting (s) dependent on a special parameter called chirality. A serious consequence of this uncertainty in electronic properties is a low fabrication yield for transistors since only s-SWCNTs are desired as the channel materials while m-SWCNTs are contaminants. Furthermore, as-grown s-SWCNTs vary in nanotube length ( $L_{\rm nt}$ ) and diameter (d). The latter property determines the electronic properties especially the bandgap ( $E_{\rm g}$ ) following a simple relationship  $E_{\rm g}\sim 1/d$  [17]. It is also difficult to precisely manipulate and translate SWCNTs due to their tiny size. Problems remain in making reproducible devices with uniform transistor performance in terms of  $I_{\rm on}$ , on/off current ratio ( $I_{\rm on}/I_{\rm off}$ ),  $V_{\rm t}$ , etc. As a consequence, in spite of their extraordinary transport properties, electronic products with large amounts of individual-SWCNT transistors are hard to realize.

Random nanotube networks comprising a large quantity of individual SWCNTs have gained particular interest because the electrical characteristics of the resultant TFTs become less dependent on the properties of individual SWCNTs. Performance fluctuation from device to device can thus be significantly reduced. In 2003, the first SWCNT-network TFTs were reported by Snow et al through a simple drop casting process and the devices exhibited excellent  $\mu$  (10 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) [21]. Later, the first medium-scale integrated digital circuits fabricated on flexible plastic foil based on SWCNTnetwork TFTs were realized [22], which has escalated the interests in the CNT technology. SWCNT-network TFTs are particularly attractive for marco- and flexible electronics since low temperature solution-based fabrication approaches can be utilized [23-30]. TABLE 1.1 gives a comparison of the SWCNT-based TFTs with other types of TFT technologies. The SWCNT-network TFTs are considered as one of the most promising candidates for marco- and flexible electronics due to their ease in fabrication and excellence in performance.

TABLE 1.1 Comparison of transistors based on different materials

|                      | Silicon          | a-Si    | Ploy-Si | Organic              | Metal<br>oxides    | SWCNTs   |

|----------------------|------------------|---------|---------|----------------------|--------------------|----------|

| Substrate            | Rigid*           | Rigid*  | Rigid*  | Flexible             | Rigid/<br>Flexible | Flexible |

| Process              | Litho-<br>graphy | Vacuum  | Vacuum  | Solution             | Sputtering         | Solution |

| Process<br>T (°C)    | High             | 150-350 | 250-550 | Low                  | RT->400            | Low      |

| Cost                 | High             | High    | High    | Low                  | Variant            | Low      |

| Mobility<br>(cm²/Vs) | 400-<br>1500     | <1      | 30->100 | 10 <sup>-5</sup> -10 | 1-100              | 10-100   |

| Stability            | Good             | Poor    | Poor    | Poor                 | Poor               | Good     |

<sup>\*</sup> It is possible to transfer devices from rigid substrates to flexible foils by the techniques developed in [8].

Despite the tremendous progress in the SWCNT-based TFTs, several important issues still await proper addressing. This includes both unveiling the underlying device physics and enhancing the device performance. For the SWCNT-network TFTs, the carrier transport is usually described by the conventional models developed for Si metal-oxide-semiconductor field effect transistors (Si-MOSFETs). It is noted that, unlike Si-MOSFETs, the electrical property of the SWCNT networks is dominated by the twodimensional (2-D) percolation pathways through the nanotube sticks from the source (S) to the drain (D) terminals [20,31,32]. The conventional models for Si-MOSFETs are unable to accurately describe the behaviors of the SWCNT networks [33,34]. One example is that the reported  $\mu$  values for the SWCNT networks extracted using the commonly used method show a large variation. This variation is closely related to the percolation geometrical parameters unique for the SWCNT networks including nanotube density  $\rho$  $(\mu m^{-2})$ ,  $L_{nt}$ , and channel length L [18,35,36]. Moreover, the gate capacitance  $(C_{\rm g})$  of the nanotube networks cannot be simplified by a parallel-plate capacitor  $(C_P)$  due to the inhomogeneity of the percolating network [21,23,37,38]. Particularly for low density nanotube networks, Cg can be seriously overestimated by using  $C_P$ , leading to an erroneous estimate of  $\mu$ . A systematic investigation and a comprehensive understanding of the physics of the percolation transport dominated nanotube networks are necessary.

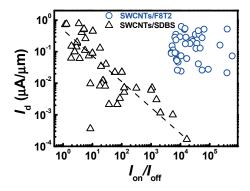

On the other hand, to improve the electrical performance of the SWCNTnetwork TFTs, a number of challenges must be overcome. The most prominent issues are: (1) poor solution processability of SWCNTs, leading to a poor fabrication yield and inferior device performance of the resultant TFTs [21]; (2) coexistence of s-SWCNTs and m-SWCNTs, resulting in difficulties in simultaneous achievement of high  $I_{\rm on}$  and large  $I_{\rm on}/I_{\rm off}$  [21,23,33,39]; and (3) huge hysteresis exhibited in the current-voltage characteristics of typical SWCNT-based TFTs due to the charging/discharging between SWCNTs and their surroundings [40,41].

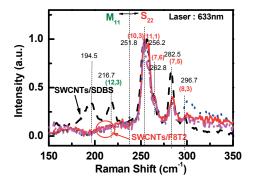

It is well-known that pristine SWCNTs are difficult to be individually dissolved in most commonly used solvents. Nanotubes tend to aggregate forming bundles due to the strong van der Waals interactions. Nanotube aggregation poses a serious hindrance to the development of solution processable TFTs. To debundle and disperse SWCNTs, a range of methods have been proposed and evaluated. They include high-concentration surfactant solutions such as sodium dodecyl sulphate [42] and the superior sodium dodecylbenzene sulphonate (SDBS) [43], DNA wrapping [25,44], and polymer wrapping such as poly(9,9-dioctylfluorenyl-2,7-diyl) (PFO) [45,46] and recently reported regionegular poly(3-alkylthiophene)s (P3AT) [47]. Among schemes. air-stable fluorene based polymer, dioctylfluorene-co-bithiophene) (F8T2), has been proven of having strong interactions with SWCNTs and capable of solubilizing SWCNTs efficiently [48]. Therefore, the combination of polymer and SWCNTs, yielding nanotube/polymer composites, is extremely interesting for solution processing of the SWCNTs.

Additionally, ordinarily synthesized SWCNTs are a mixture of m- and s-SWCNTs: about 33% metallic and 67% semiconducting. In order to attain a large  $I_{\rm on}/I_{\rm off}$ , the density of SWCNTs in the network must be in an appropriate range where the s-SWCNTs percolate but the m-SWCNTs do not [39]. However, low-density networks usually lead to low  $I_{on}$ . The difficulty in simultaneously achieving high  $I_{on}$  and large  $I_{on}/I_{off}$  sets a severe restriction on the application of such devices. Various approaches have been proposed to eliminate the m-SWCNT paths including selective synthesis [49], electrical breakdown [50], gas-phase reaction [51], selective chemical functionalization [52], lithography-assisted stripping [22], filtration to obtain y-junctions [53], dielectrophoresis [54], DNA [44] or agarose gel-assisted [55] separation, and density gradient ultracentrifugation (DGU) [56]. However, most of the methods either add difficulties in fabrication processes or lack repeatability in device performance. Recent studies suggest that, polymers, such as PFO [45] and P3AT [47], can effectively remove m-SWCNTs by centrifugation due to selective interactions and preferential binding of certain SWCNT structures by the polymer macromolecules. Hence, the use of nanotube/polymer composites may lead to s-SWCNT-enriched materials, which is essential for logic circuit applications.

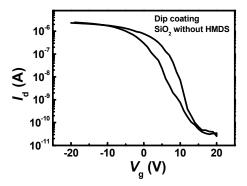

Furthermore, SWCNT-TFTs are frequently characterized by huge hysteresis in their transfer characteristics (TCs), which is represented by a giant  $V_t$  shift back and forth when the gate potential ( $V_g$ ) is swept forwardly and reversely. The presence of hysteresis complicates the understanding of device physics, e.g., it defeats the ordinary procedures for  $\mu$  extraction. It also

results in unstable operation of the TFTs, which is unacceptable in practical applications. This phenomenon is generally attributed to charging/discharging of the SWCNTs through their interactions with the surroundings, *e.g.*, water molecules bound on the SiO<sub>2</sub> surface [41,57-60] and H<sub>2</sub>O/O<sub>2</sub> in the atmosphere [41,60,61]. To combat this issue, pulsed  $I_d$ - $V_g$  methods are proposed to effectively suppress the trapping/detrapping during the measurement [62-64]. In practice, reduction of hysteresis has been realized via various methods such as SiO<sub>2</sub> surface treatment [65], suspension of the SWCNTs [66], adoption of high capacitance gate dielectric [67], passivation by organic [41,60] or inorganic materials [67], and so forth. However, all these treatments require sophisticated and expensive process conditions such as vacuum processing. An inexpensive and simple route towards hysteresisfree SWCNT-based TFTs is in strong demand.

This thesis aims to develop reliable techniques for SWCNT-based TFTs through solution processes that can offer the desired performance with (i) small hysteresis, (ii) high  $I_{\rm on}$  and large  $I_{\rm on}/I_{\rm off}$ , and (iii) excellent uniformity and dimensional scalability. A strong focus is placed on understanding of the fundamental device physics. It is hoped that working on these two aspects in parallel will lead to generation of knowledge regarding electrical behavior and fabrication techniques for nanotube/nanowire-based novel devices. The thesis is structured as follows:

Chapter 2 discusses the architectures and device physics related to the SWCNT-network TFTs. Specifically, hysteresis phenomenon in nanotube based TFTs is described.

Chapter 3 details the experimental approaches regarding the preparation of SWCNT suspensions, solution processing of the devices as well as the electrical characterization techniques. Particularly, a standard procedure to extract  $\mu$  of the nanotube TFTs is established upon a proper treatment of all the challenges. In detail,  $C_{\rm g}$  of the SWCNT-networks is determined by conducting direct capacitance-voltage (C-V) measurements on the TFTs. Hysteresis is suppressed by the adoption of a pulsed  $I_{\rm d}$ - $V_{\rm g}$  method with gate pulses of alternating polarities (AP).

Chapter 4 describes the electrical performance of the solution processed nanotube network TFTs in terms of hysteresis suppression,  $I_{\rm on}$  rise and  $I_{\rm on}/I_{\rm off}$  increase, stability, uniformity and scalability improvements. The mechanisms underlying the performance enhancements are unveiled. Finally, representative logic circuits are demonstrated based on the developed nanotube/polymer TFTs.

Chapter 5 summarizes the appended publications by also revealing the close connections among them.

Finally, Chapter 6 concludes the whole thesis and also suggests future research directions.

## 2. Fundamentals

## 2.1 Thin-film transistor (TFT) architectures

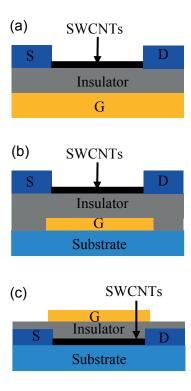

In conventional Si-MOSFETs, the gate (G) electrodes are at the surface of the devices. In contrast, the majority of SWCNT-TFTs adopt a bottom-gate configuration, in which the S/D electrodes and the semiconductor channel appear at the top of the device (Fig. 2.1(a) and (b)). This design is a natural choice for a-Si TFTs in display applications since the S/D electrodes can directly contact with the pads of the pixels. It is also an obvious choice for various sensors because the functional parts, typically the semiconductor channel, can be exposed directly to the sensing targets. Moreover, this configuration is simpler to fabricate since the SWCNT networks can be dispersed or directly grown on the insulator.

A common-gate configuration that all the designed TFTs share one gate electrode, as shown in Fig. 2.1(a), is widely used to demonstrate the concept of SWCNT-TFTs. This is mainly due to the convenience in device manufacturing. However, it is not appropriate in practice since those TFTs cannot be controlled individually to properly perform a circuitry function. Local-gate TFTs that each transistor is controlled by its own gate electrode, as displayed in Fig. 2.1(b), are therefore necessary.

Interestingly, there are few publications discussing the top-gate TFTs until recently [67,68]. In top-gate structures, the gate insulator and gate electrode are deposited on top of the semiconductor channel, as shown in Fig. 2.1(c). Recently, it is reported the dielectric layer on top of the SWCNT channel not only serves as a qualified gate insulator, but also generates an effective passivation layer for the devices [67]. Yet, it is challenging to grow insulators on top of the SWCNTs since the electronic properties of both parties, *i.e.*, insulators and SWCNTs, might be severely affected by the subsequent processes [69]. In general, it is hard to assure whether bottom-gate or top-gate is the better structure to choose. In this thesis, back-gate structures are adopted for all the SWCNT-TFTs under investigation.

The structures of the TFTs are usually optimized when engineering on the device performance. One example is the self-aligned structure which has been well established in Si technology [70]. With this structure, the overlap between the G and S/D electrodes can be ignored, leading to minimal parasitic capacitance ( $C_{\text{papa}}$ ). As a consequence, the working frequency of the devices will be significantly enhanced, as will be discussed later.

Fig. 2.1 Schematic representations for (a)-(b) bottom- and (c) top-gate SWCNT-TFTs, with (a) common- and (b) individual-gate configurations.

## 2.2 Percolation transport in nanotube networks

In an individual nanotube, if the charge transport is ballistic and the tube has perfect contacts, the conductance of the quasi 1-D nanotube is  $4e^2/h$  (155  $\mu$ S), corresponding to a resistance of 6.5  $k\Omega$  [15]. In devices, electrical contacts to an s-SWCNT are non-ideal and it leads to an additional contact resistance  $R_c$ .  $R_c$  frequently dominates the device performance because of the formation of Schottky barriers at the interface between the metal electrodes and the s-SWCNT. A series of experiments have clarified the importance of Schottky barriers in SWCNT transistors [18-20]. Javey *et al* reported a near Ohmic contact between Pd electrodes and large diameter SWCNTs (>2 nm) and ballistic SWCNT-FETs with hole mobility as high as 4000 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [19].

Although individual nanotubes have shown extraordinary  $\mu$ , devices based on single SWCNTs are difficult to manufacture and reproduce. An alternative solution is to use a large number of SWCNTs to form the channel of a TFT. This design works well especially for marcoelectronics since the TFT dimensions are usually much larger than the size of an SWCNT. In this

case, the device performance mainly depends on the collaborative and statistical distribution of the SWCNTs instead of the property of a single tube. A viable approach is to use aligned SWCNTs which are located in parallel in the channel [33,71]. However, alignment of SWCNTs requires sophisticated processes and the yield of the devices is low. As an alternative, random networks of SWCNTs, which comprise a large quantity of tubes with random orientations, are relatively easier to produce by direct growth on substrates or dispersion from solutions.

In a 2-D random SWCNT network, each tube can be treated as a rigid stick with a fixed length  $L_{\rm nt}$ . The sticks are oriented randomly in a rectangular channel with length L and width W. For a large-area TFT with  $L>>L_{\rm nt}$  and when  $\rho$  is low, the SWCNTs can only be treated as isolated "islands" in the channel region. There is no conduction pathway and the network is insulating. The SWCNT sticks start to interconnect with one other and form continuous pathways when  $\rho$  increases above the critical density  $\rho_c$  being determined by  $\rho_c$ =4.23 $^2/\pi L_{\rm nt}^2$  [31-33]. A continuous increase in  $\rho$  leads to more percolation paths and increase in the conductance.

In an SWCNT-network TFT, the carriers percolate from S to D through one or more percolating paths. Each percolating pathway consists of several sticks and the intersections between adjacent sticks. In this case, the electron transport from one stick to the adjacent one is rate-limiting in conductance instead of the charge transport in an individual tube. The drain current ( $I_d$ ) of the TFTs depends on the average path length (>L) and the total number of paths available for conduction. Therefore, increasing  $\rho$  and reducing the tube-to-tube contact resistance are two essential solutions to enhancing  $I_{on}$ . Previous studies have shown that m- (s-) SWCNTs conduct well to other m-(s-) SWCNTs, but the m-to-s contacts cause a huge resistance due to the Schottky barrier at the interface [72]. As a consequence, the conductance of the percolating networks is dominated by the tube-tube interjunctions. It is natural to treat the percolating nanotube networks as a transmission line (TL). The TL model is described in Appendix A.

It is also worth mentioning that the percolation behavior of SWCNT networks is complicated by the coexistence of m- and s-SWCNTs. In high-density SWCNT networks where a high  $I_{\rm on}$  is obtained, the majority of the SWCNTs percolate including the undesired m-SWCNT pathways, leading to a significant degradation in  $I_{\rm on}/I_{\rm off}$ . In contrast, low-density networks can avoid the contamination of the m-SWCNTs and ensure a relative large  $I_{\rm on}/I_{\rm off}$ . However,  $I_{\rm on}$  is generally low due to the limited number of percolation paths. Thus, it is difficult to achieve both high  $I_{\rm on}$  and large  $I_{\rm on}/I_{\rm off}$  in the presence contaminating m-SWCNTs. This sets one of the major obstacles for SWCNT-TFTs. By carefully tailoring the shape of the networks, for example, long strips [20] or Y-junction long nanotubes [46], higher  $I_{\rm on}/I_{\rm off}$  can be obtained with a network of relatively denser SWCNTs. However, the most effective method is to increase the fraction of s-SWCNTs. Theoretical

calculations indicate that  $I_{\rm on}/I_{\rm off}$  can be immune to the presence of m-SWCNTs when the fraction of s-SWCNTs exceeds 90% [39].

### 2.3 Electrical characteristics of SWCNT-network TFTs

#### From the "top-down" view

At present, the electrical models of Si-MOSFETs are widely used for describing the operation of TFTs and analyzing the carrier transport in the devices. Similar to organic TFTs [6], the  $I_{\rm d}$ - $V_{\rm g}$  behavior of the SWCNT-network TFTs can be modeled by a traditional "top-down" approach in which the network is treated as a homogeneous bulk material. In this model, the TFTs turn on when  $V_{\rm g}$  is higher than  $V_{\rm t}$ . At low drain bias ( $V_{\rm d}$   $V_{\rm g}$ - $V_{\rm t}$   $V_{\rm d}$   $V_{\rm d}$

$$I_{d} = \mu C_{g} \frac{W}{I} (V_{g} - V_{t}) V_{d}$$

(2.1)

$I_{\rm d}$  saturates at higher  $V_{\rm d}$  ( $V_{\rm d} \ge V_{\rm g}$ - $V_{\rm t}$ ) and it can be represented by,

$$I_{\text{dsat}} = \mu C_{\text{g}} \frac{W}{2L} (V_{\text{g}} - V_{\text{t}})^2$$

(2.2)

### From the "bottom-up" view

The classical model simplified in equations (2.1) and (2.2) usually focuses on uniform materials and indicates a current scaling relationship in form of  $I_{\rm d}$   $\propto$  1/L. However, the percolating SWCNT networks are inhomogeneous in terms of  $L_{\rm nt}$ , L, and  $\rho$ , indicating the inadequacy of using these equations to model the TFT behaviors or estimate the device performance. As shown Fig. 2.2(a), for a network with a certain  $\rho$ , only the SWCNTs lying in the percolation paths (yellow dotted lines) contribute to  $I_d$ , while the SWCNTs not in the percolation paths are inactive to current conduction. When L is reduced by a factor of n (n>1), the original SWCNTs taking part in percolation are still conductive and contribute to a current of  $nI_d$ . Meanwhile, part of the SWCNTs that were isolated previously may now become part of the bridge between S and D as shown in Fig. 2.2(b) (the red dashed line), and thus contribute to an additional current  $\Delta I_{\rm d}$ . The total current will therefore be higher than  $nI_d$ . In other words, the traditional electrical model from the "top-down" view is inadequate in analyzing a 2-D nanotube network. Instead, a "bottomup" approach that takes the percolation geometry of the nanotube networks into consideration is proposed and developed [31,34]. In this model, the stick percolating networks satisfy the following finite-size scaling relationship [34],

$$I_{d} = \frac{A}{L_{nt}} \xi \left( \frac{L_{nt}}{L}, \rho L_{nt}^{2} \right) \times f\left(V_{g}, V_{d}\right)$$

(2.3)

where the proportionally constant A depends on  $C_{\rm g}$ , tube diameter d, and stick–stick interaction parameter. Function  $\xi$  represents the geometrical contribution with parameters  $L_{\rm nt}$ , L, and  $\rho$  while function f is more of the electrical contribution including the effects of  $V_{\rm g}$  and  $V_{\rm d}$ . It is found that equation (2.3) is universal for arbitrary geometrical and biasing conditions.

For long channel TFTs with  $L>>L_{nt}$ , the carriers travel through the intersects of nanotubes and diffusive transport dominates. The electrical contribution function f can be expressed by,

$$f\left(V_{g}, V_{d}\right) = \left(V_{g} - V_{t}\right) V_{d} - \beta V_{d}^{2}$$

(2.4)

where  $\beta$ =0.5. And the geometrical scaling function  $\xi$  is,

$$\xi\left(\frac{L_{\rm nt}}{L}, \rho L_{\rm nt}^2\right) = \left(\frac{L_{\rm nt}}{L}\right)^{m(\rho L_{\rm st}^2)} \tag{2.5}$$

where m is the current scaling exponent which only depends on the network coverage p. Here,  $p=\rho L_{\rm nt}^2$ . m decreases monotonically with increasing p. The simulation results [33] show that for high coverage networks (e.g.,  $p \ge 19$ ),  $\xi$  approaches the classical limit with m=1. For a sparser network with p near the percolation threshold  $p_c=4.236^2/\pi \approx 5.7$  [31], m>>1.

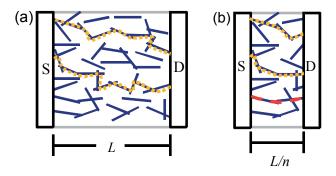

Fig. 2.2 (a) A percolating SWCNT network with channel length of L. The yellow dotted lines represent two percolation pathways. (b) When L is reduced to L/n, an additional percolation path occurs as indicated by the red dashed line.

## 2.4 Hysteresis in SWCNT-based TFTs

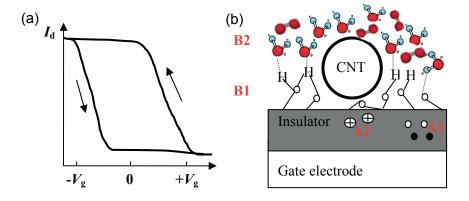

Hysteresis appears as a result of  $V_{\rm t}$  variation with the range, speed, and direction of  $V_{\rm g}$  sweep (Fig. 2.3 (a)). It is unfortunately a commonly observed phenomenon in SWCNT-based transistors [40,41]. This phenomenon was also frequently observed in the Si/SiO<sub>2</sub> system in the early days of Si-MOSFETs primarily induced by the presence of mobile ionic charges like Na<sup>+</sup>, Li<sup>+</sup>, K<sup>+</sup>, and H<sup>+</sup> in the gate dielectric (*i.e.*, SiO<sub>2</sub>) [74]. It led to delay of the practical application of Si-MOSFETs. Hysteresis can be effectively developed into memory devices [40]. But in most other cases, even a small degree of hysteresis is detrimental and hence unwanted. Thus, it is a critical parameter although much less discussed compared with other issues such as  $\mu$ .

In SWCNT-based transistors, hysteresis is observed in both individual tube and network devices. Recently, more focus has been put to unveil the underlying mechanisms [41,57-61]. The reported sources of hysteresis in the literature can be summarized in Fig. 2.3(b): (A1) oxide trapped charges (holes or electrons), (A2) mobile oxide charges (ionic impurities) [74], (B1) interface traps between the SWCNT channel and the gate insulator, including the well-discussed and widely-accepted oxide surface bound -OH groups [41,57-60], and (B2) environmental adsorbents particularly H<sub>2</sub>O and O<sub>2</sub> molecules [41,60,61].

Particularly, for TFTs with  $SiO_2$  as the gate insulator, hysteresis of the SWCNT-based transistors primarily originates from mechanisms B1 and B2. The  $SiO_2$  surface-bound water molecules ( $Si\equiv OH$ ) serve as electron traps at the interface. The charging/discharging of these traps by carriers in the

Fig. 2.3 (a) Schematic TCs and (b) sources of hysteresis for the SWCNT-based transistors.

channel region electrostatically modulates the SWCNTs, thereby changing the current level of the devices. Initially in the off-to-on (reverse) sweep where  $V_{\rm g}$  is positive, electrons are trapped by those Si $\equiv$ OH groups. When  $V_{\rm g}$  sweeps toward negative direction, more holes are attracted to balance the virtual gate induced by the trapped charges. These excess holes result in an increased  $I_{\rm d}$ . In contrast, the on-to-off (forward) sweep starts with a negative  $V_{\rm g}$  and the trapped electrons are emptied quickly. Thus, a lower  $I_{\rm d}$  is observed when  $V_{\rm g}$  sweeps form negative to positive (Fig. 2.3(a)). The physisorbed  $H_2{\rm O/O_2}$  molecules around the SWCNTs severely influence the density of the Si $\equiv$ OH groups [60,61] and therefore the degree of hysteresis in the devices. This explains why hysteresis is more pronounced in a humid environment [75].

To suppress hysteresis, annealing the samples under vacuum can reduce the density of water molecules [41]. Surface treatment with hydrophobic self-assembly monolayers (SAMs) such as octadecyltrichlorosilana (OTS) [65] or dielectrics, *e.g.*, divinyltetramethyl siloxanebis-(benzocyclobutene) derivative [58], would lead to an –OH free surface. Suspending the SWCNTs can avoid the interface with SiO<sub>2</sub>. Other methods including encapsulation with poly(methyl methacrylate) (PMMA) [41] or Methylsiloxane [60] could effectively passivate the surrounded trap sites.

# 3. Experimental Approaches

## 3.1 Dispersion of nanotubes in solution

The basic requirement for solution process is a stable solution or suspension of the electronic materials. In our experiments, dissolving nanotubes by surfactant and polymer wrapping are the two methods investigated to prepare the SWCNT suspensions.

#### 3.1.1 Surfactant aided solubilization

The hydrophobicity of the SWCNT surface can be altered via surface wrapping by surfactants such as SDBS. The SDBS molecule comprises two parts with one terminal being hydrophobic (-CH3) and the other hydrophilic. The strong interaction between the benzene ring in the SDBS molecule and the  $sp^2$  hybridization structure of the SWCNTs enables the wrapping of the surface of SWCNTs. Meanwhile, the hydrophilic terminals provide steric repulsion on the SWCNTs and effectively stabilize them in the solvent.

To prepare a water-based SWCNT suspension, as received HipCo SWCNTs from Unidym (average diameter 1.1 nm) were bath-ultrasonically added into de-ionized water containing 1 wt.% SDBS followed by tip-sonication. Then, the suspension was centrifuged at 16000 g overnight. The upper 70% of the supernatant was carefully collected for TFT fabrication. This method is widely used in the research community and further developed by multiple DGU steps to separate the m- and s-SWCNTs in solution [56].

However, it is noted that the surfactants contain a great deal of impurities, e.g., Na<sup>+</sup>. The utilization of high-power sonication also creates defects in C-C bonds as well as trims the tubes into short segments. Consequently, the electronic properties of the SWCNTs are adversely affected, which is undesired for TFT applications. Dispersion of SWCNTs without degradation of the material is in strong demand.

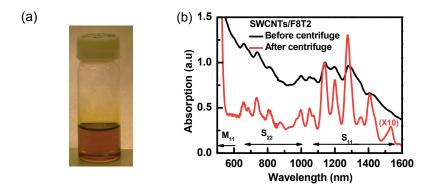

## 3.1.2 Polymer aided solubilization

A number of polymers have been identified to assist dispersion of SWCNTs in various media [45-48]. In contrast to the surfactant method that all the tubes are coated, polymer macromolecules usually preferentially wrap a certain type of nanotubes with certain diameters or chirality. Hence, highly

selective solubilization can be achieved. An air-stable aromatic polymer, F8T2, is selected in our work to disperse the SWCNTs. The F8T2 molecules contain fluorene rings in the backbones which are close to the surface structure of SWCNTs. The strong  $\pi$ - $\pi$  stacking between SWCNTs and the polymer can enable a good wrapping outcome. Experimentally, around 2–3 mg as received HiPco-SWCNTs were ultrasonically added into a 50-mL F8T2 solution in toluene (0.2 mg/mL). Then, the mixture was utilized for device fabrication by simple dilution. Alternatively, it was centrifuged at 13300 g for 60 min and the supernatant was used as the starting material for device manufacturing.

#### 3.2 TFT fabrication

### 3.2.1 Substrate preparation

#### Common back-gate structure

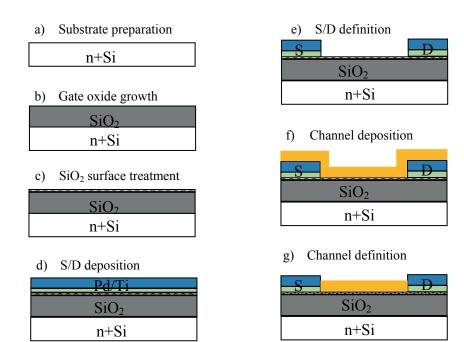

As described in Section 2.1, the common back-gate configuration (Fig. 2.1(a)) is the most convenient structure for testing the electrical behavior of new semiconducting materials. The process flow to fabricate the TFTs is schematically illustrated in Fig. 3.1. It started with heavily n-type doped Si wafers as the substrate as well as the gate electrode. Then, a thermally grown 150-nm SiO<sub>2</sub> layer served as the gate insulator. Afterwards, the SiO<sub>2</sub> surface was functionalized by a Hexamethyldisilazane (HMDS) SAM layer by loading the whole wafer into an oven at 110 °C for 30 min, which is commonly used in Si-technology for improving the adhesion of photoresist during lithography processing. In CNT technology, the surface functionalization can be also achieved by utilizing 3-aminopropyltriethoxysilane (APTS), that is believed to significantly enhance the adhesion of SWCNTs [76]. To coat a monolayer of APTS, the whole wafer was immersed into 1 mL APTS in Chloroform for 30 minutes followed by baking at 110 °C for 10 minutes. After that, the S and D electrodes comprising a bi-layer of 35-nm Pd on top of 5-nm Ti were defined by electron-beam evaporation (EBE) followed by a standard lift-off procedure. The gap between the S and D electrodes, i.e., L, was varied from 5 to 200 μm. The channel area was then opened in a newly coated 1.2-µm-thick photoresist layer. Then the substrate is ready for the formulation of the channel material to bridge the gaps between S and D.

#### Local back-gate structure

The structure of an individual back-gate TFT was designed as shown in Fig. 2.1(b). Metal islands consisting of a tri-layer metal stack, *i.e.*, 1-nm Al/40-nm Au/10-nm Ti, serving as individual back-gate electrodes, were grown on  $SiO_2$  by combining EBE with lift-off. The thin Al film was easily oxidized in the presence of  $O_2$ , serving as the nucleation layer for the subsequent growth

Fig. 3.1 Schematic representation of the fabrication process for a common back-gate SWCNT-based TFT.

of gate dielectric by means of the atomic layer deposition (ALD) process [77]. A 10-nm thick ALD AlO $_x$  was grown at 300  $^{\circ}$ C using trimethylaluminum (TMA) and  $H_2O$  as the reaction precursors. Similar to the TFTs with the  $SiO_2$  gate insulator, the  $AlO_x$  surface was functionalized with HMDS followed by the construction of the S/D electrodes. Finally, the channel area was opened in a newly coated photoresist layer

#### 3.2.2 Channel formation

#### **Drop** casting of aqueous solution

By simple drop-casting to deposit the SWCNT aqueous solution on top of the chips with pre-defined S/D electrode pairs, SWCNT random networks were obtained. After water evaporation and removal of photoresist in Acetone, SWCNT network channels were formed and TFT fabrication completed.

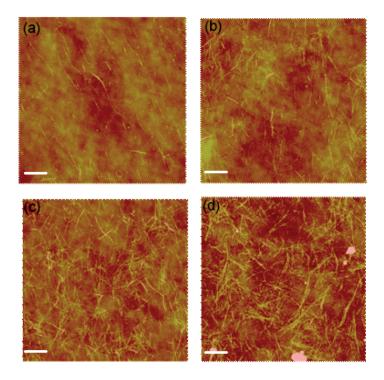

Fig. 3.2 AFM images of SWCNT networks with different p: (a) 1.8, (b) 6.5, (c) 9.9, and (d) 16.6. The scale bars are 1  $\mu$ m.

SWCNT networks with various nanotube densities imaged by means of atomic force microscopy (AFM) are shown in Fig. 3.2. The surface coverage p of the networks was obtained by counting the number of the SWCNTs in the images and measuring the length of the tubes. Obviously, when p is low (1.8) as shown in Fig. 3.2(a), nanotubes are isolated from each other. With increasing p (6.5 in (b)), SWCNTs contact with each other and percolation pathways eventually form in the channel region. Further increase of p (9.9 in (c)) leads to more percolation routes. When the density of SWCNTs is high, as shown in Fig. 3.2(d) with p=16.6, the SWCNTs start to agglomerate. Although the drop-casting method is extremely simple, it lacks repeatability and is of low yield due to the poor controllability. In our experiments, the best yield for the conducting TFTs is around 70% but the devices show unacceptable performance variations.

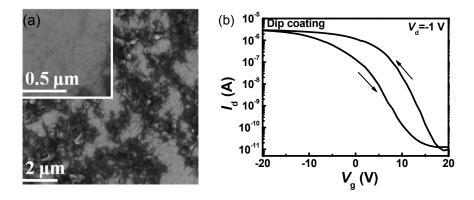

## Spin-/dip-coating of nanotube/polymer composites

Both spin- and dip-coating methods are widely used in organic device fabrications. Compared with drop casting, these two methods are more controllable. During spin-coating, an excess amount of SWCNT/F8T2 solution is

placed on the substrate surface. The substrate wafer is then set to rotate at high speed in order to spread the fluid by the centrifugal force. The morphology of the thin film formed is strongly dependent on the spin speed and duration. For instance, spin-coating the SWCNT/F8T2 mixture at 2000 rpm (revolutions per minute) for 30 sec typically results in 10-20 nm thick composite films. Extremely thin films, assumed to be monolayer, could be obtained by further increasing the spin speed. With spin-coating, the yield for conducting devices can approach 100%.

Dip-coating provides an alternative route for depositing uniform thin films. Recently, it has been shown that higher  $\mu$  can be achieved if the organic film is deposited by dip-coating instead of spin-coating [78]. In our experiments, the chip was simply immersed in the SWCNT/F8T2 composite solution (the supernatant after centrifugation) and kept stewing for 5-10 hours in ambient conditions. It was then pulled out from the solution carefully to avoid jitters. The composite deposited itself on the substrate. SWCNT/F8T2-TFTs with both  $SiO_2$  and  $AlO_x$  as gate insulator were successfully fabricated by such a facile dip-coating process. Compared with the SWCNT/F8T2-TFTs fabricated by spin-coating, dip-coating provides comparatively thicker composite films and better surface coverage in the channel. This feature renders outstanding device performance in terms of hysteresis elimination,  $I_{on}$  increase, as well as uniformity improvement, as will be discussed in Chapter 4.

#### **Inkjet printing of the composites**

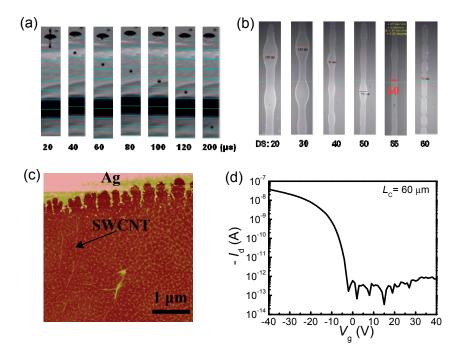

By an additional step of filtration with a membrane of pores 0.2 mm in diameter for the SWCNT/F8T2 mixture, we have performed inkjet printing of the composite solution on a Dimatix desktop inkjet printer [79]. As shown in Fig. 3.3(a), the drops of the SWCNT/F8T2 composite are jetted at a uniform velocity of 5 m/s, implying a proper viscosity and surface tension of the composite solution.

In printing electronics, the desired printed lines would be smooth, even, narrow, and straight. However, the printing process itself is dependent on a range of parameters such as substrate temperatures, drop frequencies, and drop spacing (DS) [80]. In Fig. 3.3(b), by carefully tailoring DS during parameter optimization, various line morphologies on  $SiO_2$  substrate are obtained. When DS is as small as 20  $\mu m$ , discreet bulges along the line length separated by segments of uniform narrow lines are observed. This can be attributed to the outflow of the additional fluid during printing. With increasing DS, the bulges become narrower. This tendency persists until DS is reduced to 55  $\mu m$  where a smooth and straight track is obtained. These lines have uniform smooth edges and tops, along with the narrowest width of  $\sim$  60  $\mu m$ . With a further decreased DS, for instance, at 60  $\mu m$ , the drops are too far to interact with each other, leading to islands in the patterns.

Subsequently, inkjet-printed SWCNT/F8T2 TFTs were fabricated with heavily doped n<sup>+</sup>-Si as the gate electrode and 150 nm SiO<sub>2</sub> as the gate insulator. The S/D electrodes were inkjet-printed using a commercial available Cabot CCI-300 conductive ink containing 19-21 % weight of nano-silver particles. The topview image by AFM of the composite film beside one of the Ag electrode is shown in Fig. 3.3(c). It is found that the long, curved SWCNTs are lying in the matrix of F8T2. Although the concentration of the nanotubes in the thin film is so low that the SWCNTs are non-percolated,  $I_{\rm on}$  of the TFTs is still enhanced due to the presence of the highly conductive SWCNTs embedded in the polymer matrix [84]. In Fig. 3.3(d), TC of an inkjet-printed SWCNT/F8T2-TFT with L=60  $\mu$ m and W=100  $\mu$ m is depicted.  $I_{\rm on}$ / $I_{\rm off}$ >10<sup>5</sup> is achieved, which has the potential for logic circuit applications. It is expected that further optimization on the formulation of the composite ink would lead to continuous improvements of the electrical performance.

Fig. 3.3 (a) Optical image of the SWCNT/F8T2 drops during jetting process. (b) Line patterns of the SWCNT/F8T2 composite with various drop spacings. (c) An AFM image in height mode of an inkjet-printed SWCNT/F8T2 composite film. (d) A TC of an inkjet-printed SWCNT/F8T2-TFT with  $V_{\rm g}$  scanned from -40 to +40 V and  $V_{\rm d}$  fixed at -2 V. W and  $V_{\rm d}$  of the TFTs were 60 and 100  $\mu$ m, respectively.

## 3.3 Electrical characterizations

## 3.3.1 Hysteresis suppression by pulsed $I_{\rm d}$ - $V_{\rm g}$ method

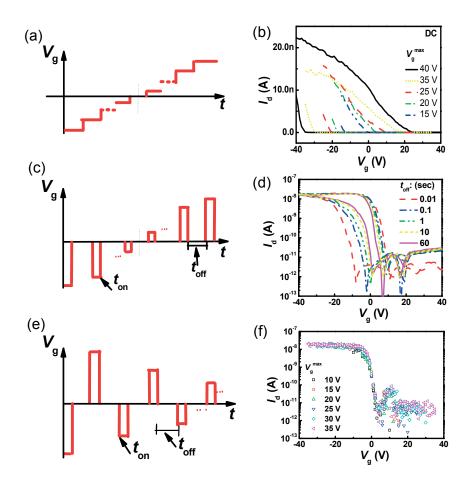

The TCs of the SWCNT-based TFTs were characterized through a semiconductor analyzer (Agilent 4156C or Keithley 4200SCS). In conventional  $I_{\rm d}$ - $V_{\rm g}$ measurement,  $V_{\rm g}$  is continuously swept step by step as shown in Fig. 3.4(a). At each step, the bias is held for a certain period of time to ensure an accurate measurement, particularly for small current. In the presence of charging/discharging effects with a time constant comparable with the measurement time, the trapped charges can serve as an additional virtual gate that modulates the carriers in the channel region. In a DC sweep, the charges remain trapped until the gate polarity is switched, thereby leading to the widely observed hysteresis in the TCs of the SWCNT-TFTs. Fig. 3.4(b) presents the  $I_{\rm d}$ - $V_{\rm g}$  characterization results of an SWCNT-network TFT with p=6.5 in DC mode. When  $V_{\rm g}$  is swept forwardly and reversely, a huge gap is observed. The hysteresis gap can be defined by  $\Delta V_{\rm H} = V_{\rm t}^{\rm r} - V_{\rm t}^{\rm f}$  with  $V_{\rm t}^{\rm r}$  and  $V_{\rm t}^{\rm f}$ the  $V_{\rm t}$  values obtained from the reverse and forward TCs. Obviously,  $\Delta V_{\rm H}$ increases continuously with increasing the measurement range  $(V_{\mathrm{g}}^{\mathrm{max}})$  and reaches about 56 V at  $V_{\rm g}^{\rm max}$ =40 V.

A conventional pulsed (CP)  $I_d$ - $V_g$  measurement method was conducted by measuring  $I_d$  at each data point for a dwell time of  $t_{on}$  followed by a period during which  $V_{\rm g}$  returned to zero ( $t_{\rm off}$ ), as indicated in Fig. 3.4(c). The trapped charges could effectively relax when  $V_{\rm g}$  bias was removed. Thus,  $\Delta V_{\rm H}$  was significantly reduced. A shorter  $t_{\rm on}$  and longer  $t_{\rm off}$  is expected to lead to smaller  $\Delta V_{\rm H}$ . In 2006, Lin, et al reported that pulsed measurements with a time constant below 500 µs provided reproducible TCs of TFTs based on individual SWCNTs [85]. Later, small  $\Delta V_{\rm H}$  was obtained for SWCNT transistors by applying pulsed  $I_{\rm d}$ - $V_{\rm g}$  measurements with  $t_{\rm off}$  as long as 10 sec in vacuum [62]. As shown in Fig. 3.4(d), much narrower gaps were obtained by CP method compared with DC. As expected, smaller  $\Delta V_{\rm H}$  is observed with longer  $t_{\rm off}$ . It is reported that the characteristic time constant for charge detrapping is around 8 s [63]. In Fig. 3.4(d), it is found that  $\Delta V_{\rm H}$  drops to about 6 V for  $V_{\rm g}^{\rm max}$ =40 V with  $t_{\rm off}$  =60 s. However, the residual  $\Delta V_{\rm H}$  is rather persistent and difficult to be completely eliminated in ambient, indicating that  $V_{\rm g}$  pulses of the same polarity still cause the charge accumulation during a sweep loop.

Alternatively, a pulsed sweep method by using gate pulses of alternating polarities (AP) as shown in Fig. 3.4(e) was introduced to suppress hysteresis [64]. In this method, a negative pulse is applied followed by a positive one of the same amplitude and duration. The charge trapped in the positive pulse could now be driven out in the followed negative one. Thus, the hysteresis can be effectively suppressed. As shown in Fig. 3.4(f), hysteresis-free TCs can indeed be obtained when the AP method is applied. With AP method, all

the TCs merge and can be recognized as the intrinsic property of the TFTs. Moreover, this method is extremely interesting since it avoids the requirements of expensive fast instruments or long waiting time as is necessary for the CP method. In **Paper II**, similar results were obtained with an SWCNT-network TFT with p=9.9.

It is worth mentioning that those pulsed  $V_{\rm g}$  methods can be also transferred to C-V measurements in order to suppress the hysteresis presented in C-V curves (see Section 3.3.2).

Fig. 3.4 Sketches for  $I_{\rm d}$ - $V_{\rm g}$  measurements and TCs for an SWCNT-TFT with p=6.5 in (a, b) DC, (c, d) CP, and (e, f) AP modes, respectively. For all the measurements,  $V_{\rm d}$ =-1 V.

## 3.3.2 Gate capacitance $(C_g)$ of networked nanotubes

Gate capacitance  $C_g$  is a crucial parameter for transistors since it is the measure of gate control over the channel conductance as well as the basis to extract  $\mu$  and estimate the transient behavior of devices and integrated circuits. An accurate determination of  $C_g$  is of paramount importance for SWCNT-TFTs as well. In early studies,  $C_g$  of the SWCNT-network TFTs is approximated by the capacitance of a parallel-plate system,  $C_P$ , which is simply determined by  $C_P = \varepsilon_0 \varepsilon_{ox}/t_{ox}$  with  $t_{ox}$  as the gate oxide thickness,  $\varepsilon_0$  and  $\varepsilon_{ox}$  the relative permittivity of the gate insulator and the permittivity in vacuum [81]. However, unlike Si-MOSFETs in which the semiconducting channel is homogeneous, the conduction of the nanotube networks is determined by the stick-percolation which depends strongly on the geometrical parameters [31-34] as discussed extensively earlier. Thus, use of  $C_P$  can lead to an erroneous estimation of  $C_g$ . More rigorously,  $C_g$  of the nanotube networks can be calculated by examining the metal-insulator-semiconductor (MIS) capacitor with consideration of the electrostatic coupling between the nanotubes [37,38], which leads to an analytical expression for calculation of  $C_{\rm g}$ [38],

$$C_{\rm g} = \left\{ C_{\rm Q}^{-1} + \frac{1}{2\pi\varepsilon_{\rm o}\varepsilon_{\rm ox}} \ln\left[\frac{\Lambda_{\rm o}}{R_{\rm nt}} \frac{\sinh(2\pi t_{\rm ox}/\Lambda_{\rm o})}{\pi}\right] \right\}^{-1} \Lambda_{\rm o}^{-1}$$

(3.1)

where  $C_Q$ =4.0 X 10<sup>-12</sup> F/cm is the quantum capacitance of the nanotubes [82], 1/ $\Lambda_0$  is the nanotube density ( $\mu m^{-1}$ ) in the network , and  $R_{\rm nt}$  is the radius of the tubes. This model was widely adopted in the literatures thereafter [24-28,53]. However, complications arise since the calculated  $C_{\rm g}$  value is very sensitive to R and 1/ $\Lambda_0$  used in equation (3.1). But they are both difficult to quantify for a random network with large amounts of nanotubes.

Experimentally, the capacitance of an individual SWCNT was measured in 2006 by directly performing C-V measurements on a top-gated FET configuration with a single nanotube as the conduction channel [83]. For SWCNT networks, the measurement of  $C_{\rm g}$  is still controversial. To characterize  $C_{\rm g}$  of the SWCNT-network TFTs, Cao *et al.* executed C-V measurements on a dish-shaped MIS capacitor formed by gold, HfO<sub>2</sub>, and SWCNT networks, giving rise to a measured  $C_{\rm g}$  being about one third of the capacitance of the HfO<sub>2</sub> [22].

For a percolating network, only those nanotubes in the percolation pathways contribute to the current conduction. It is therefore natural to suggest that  $C_{\rm g}$  only takes the contributions of the percolated SWCNTs into account. However, the measurement on a MIS structure includes those SWCNTs that do NOT contribute to the current conduction, consequently leading to an overestimation of  $C_{\rm g}$ . A direct C-V measurement on the TFT configuration provides a more sensible and accurate determination of  $C_{\rm g}$  of the nanotube

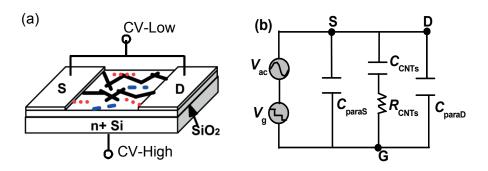

networks [29]. The C-V measurement setup for this novel measurement arrangement on the SWCNT-network TFTs with its equivalent circuit is illustrated in Fig. 3.5. The G electrode of the TFT is connected to the CV-High terminal while the S and D are both connected to the CV-Low terminal of the LCR meter (HP4284A from Agilent), as shown in Fig. 3.5(a). During C-V measurements, a small AC signal at a measurement frequency of  $f_{\rm m}$  is superimposed to the DC bias  $V_{\rm g}$ . The parasitic capacitance, mainly originated from the overlap between G and S/D electrodes, can be determined by measuring on the TFT structure without any nanotubes in the channel. Then, the capacitance of the SWCNTs can be calculated by subtracting the parasitic capacitance from the total capacitance measured from the TFTs (cf. Fig. 3.5(b)).

With the consideration of the percolation behavior and the measured capacitance by the direct *C-V* measurement on TFT configurations, the nanotubes in the percolating network can be divided into 3 categories as depicted in Fig. 3.5(a): (i) percolated nanotubes (black solid lines) that contribute to both conductance and capacitance; (ii) isolated nanotubes (blue dashed lines) lying in the channel region by themselves that contribute to neither capacitance nor conductance; and (iii) non-percolated tubes but connected with the S/D electrodes or the percolation pathways that contribute to capacitance but not to conductance.

Cleary, MIS structures include all the 3 classes of nanotubes, which would overestimate  $C_g$ . The measured capacitance through direct C-V measurements on TFTs solely contains type (i) and (iii). The isolated ones (type (ii)) are effectively excluded. This is more accurate compared to the MIS

Fig. 3.5 (a) Sketch of the C-V measurement setup on an SWCNT-network TFT. The stick percolation network consists of (i) percolated tubes (black solid lines), (ii) isolated tubes (blue broken lines), and (iii) tubes connected to the S/D electrodes or the percolating pathways but non-percolated (red dotted lines). (b) Equivalent circuit of the C-V measurement arrangement.

structures. Moreover, the Monte Carlo simulation shows that the non-percolated nanotubes (type (iii)) are insignificant for the total amount of the SWCNTs (**Paper I**). Thus, a more reliable measurement of  $C_g$  is established.

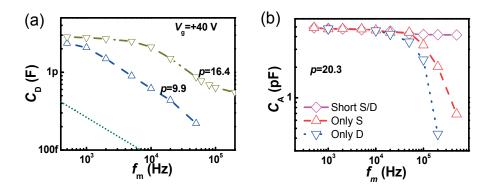

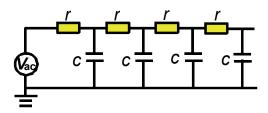

#### Dependence of $C_g$ on measurement frequency

In Paper I, C-V measurements were performed directly on SWCNT-network TFTs at different  $f_{\rm m}$ . A consistent tendency is found that the accumulation capacitance  $C_{\rm A}$  (extracted at  $V_{\rm g}$ =-40 V) stays constant at low  $f_{\rm m}$  and starts to drop over a critical frequency  $f_{\rm c}$ . In addition, the frequency dispersion of the measured capacitance is quantitatively analyzed by the RC TL model described in Appendix A. The good agreement of the measured  $f_{\rm c}$  values with the ones calculated from equation (A.8) confirms the validity of the TL model. Therefore,  $C_{\rm g}$  of the SWCNT-network TFTs can be effectively extracted in the low frequency region where no TL effect occurs.

For SWCNT-network TFTs, the channel resistance in the depletion region  $R_{\rm off}$  is much higher than that in the accumulation region  $R_{\rm on}$ . According to the TL model,  $f_{\rm c} \propto R^{-1}$ . It is expected that  $f_{\rm c}$  for depletion capacitance  $C_{\rm D}$  is much lower than that for  $C_{\rm A}$ . Fig. 3.6(a) shows the frequency response of  $C_{\rm D}$  (extracted at  $V_{\rm g}$ =+40 V) for TFTs with p=9.9 and 16.4. It is found that  $f_{\rm c}$  is  $\sim$ 5 kHz for  $C_{\rm D}$  when p=16.4, which is significantly lower than that of  $C_{\rm A}$  ( $\sim$ 80 kHz, in **Paper I**). Similar result is found for  $C_{\rm D}$  and  $C_{\rm A}$  of the TFT with p=9.9. Hence, a larger difference in  $C_{\rm A}$  and  $C_{\rm D}$  of a device with the 150-nmthick SiO<sub>2</sub> gate insulator is found in **Paper I** compared with a device with a 30-nm-thick SiO<sub>2</sub> gate insulator [84]. The green dotted line has a decaying slope of -1/2, implying the validity of the TL effect once again.

Fig. 3.6 (a)  $C_{\rm D}$  (extracted at  $V_{\rm g}$ =+40 V) as a function of  $f_{\rm m}$  for the TFTs with p=9.9 and 16.4. (b)  $C_{\rm A}$  as a function of  $f_{\rm m}$  for the TFTs with p=20.3 with different connection setups.

As discussed in **Paper I**, the root of TL effect is carrier injection from the electrodes to the nanotubes in the channel region. Once there is nanotubes have connections with electrodes, TL effect exists. We have further tested the frequency response of a TFT (p=20.3) with  $V_g$  applied between G and only S (D) electrode, with D (S) floating, as shown in Fig. 3.6(b). It can be seen that with only S (D) setup, the capacitance also possesses frequency response with a lower  $f_c$ .

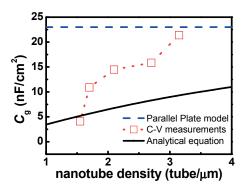

#### Dependence of $C_g$ on nanotube density

Intuitively, the capacitance of the percolating networks increases with increasing nanotube density. Theoretical calculations indicate that the increase of  $C_{\rm g}$  with  $\rho$  continues until the distance between the nanotubes is approximately the same as the thickness of the gate insulator [21]. In **Paper I**,  $C_{g}$  is more accurately obtained through direct C-V measurements in the region of  $f_{\rm m} < f_{\rm c}$  in order to avoid the TL effects. Fig. 3.7 shows the measured  $C_{\rm g}$  with different nanotube densities. It is clear that a higher  $C_{\rm g}$  is obtained for devices with a denser network (denoted as red rectangular). It is also observed that C<sub>g</sub> extracted with the absence of the TL effect is considerably smaller than  $C_{\rm P}$  (denoted by blue dashed line in Fig. 3.7). Furthermore, compared with  $C_{\rm g}$ calculated using equation (3.1), the measured  $C_{\rm g}$  is even higher. This is attributed to the difficulties in determining the geometrical parameters in equation (3.1). The effective area of the SWCNT networks, evaluated by  $C_g/C_P$ , approaches 1 for a sufficiently dense film. In this region, the utilization of an MIS structure is a proper simplification. While for a film with low-density nanotubes,  $C_{\rm g}/C_{\rm P}$ <1 and the extracted mobility via  $C_{\rm P}$  would be severely underestimated.

Fig. 3.7  $C_g$  of the SWCNT-network TFTs as a function of nanotube density.  $C_g$  obtained from  $C_P$  (blue dashed line), equation (3.1) (black solid line), and direct C-V measurements (red rectangular) are included for comparison.

### 3.4 Mobility ( $\mu$ ) extraction

Carrier mobility  $\mu$  is one of the most important indicators of device performance.  $\mu$  of the SWCNT-network TFTs could be extracted by referring to the traditional model for Si-MOSFETs expressed in equation (2.1), as many did in earlier days of nanotube research [81]. However, it has been found that the reported  $\mu$  values for the SWCNT-based TFTs suffer from huge variations, leading to the great difficulties in making a sensible assessment within the research communities [18,35,36]. Surprisingly, the variations are not only dependent on process differences but also the geometrical parameters such as L,  $\rho$ , and  $L_{\rm nt}$ .

In general, the challenges in  $\mu$  extraction involve the following aspects. Firstly, the effective  $C_{\rm g}$  of a stick-percolating network is lower than  $C_{\rm P}$ , particularly for low-density nanotube networks (Section 3.3.2). Secondly, the transport of SWCNT-network TFTs scarcely satisfies the relation  $I_{\rm d} \propto 1/L$  (Section 2.3). Thirdly, TCs of SWCNT-network TFTs frequently suffer from substantial hysteresis (Sections 2.4 and 3.3.2). Therefore, a new procedure to extract  $\mu$  by addressing all these challenges is necessary.

#### 3.4.1 Dependence of $\mu$ on hysteresis

The validity of  $\mu$  extraction by equation (2.1) is based on the assumption that the transconductance  $g_m$  can be unambiguously determined. Since  $g_m$  is the first derivative of the  $I_d$ - $V_g$  curve,  $V_t$  should not be related to  $V_g$ . In Fig. 3.4(b), it is obvious that  $V_t^f$  extracted from the TCs in DC mode increases with increasing  $V_g^{\text{max}}$ . The opposite is true for  $V_t^r$  as it decreases with increasing  $V_g^{\text{max}}$ . An invariant  $V_t$ , *i.e.*, a hysteresis-free  $I_d$ - $V_g$  characteristics is essential for the extraction of  $\mu$ . This issue has been, unfortunately, undermined in a large number of publications that have made direct extraction of  $\mu$  without clarifying their sweep conditions.

TABLE 3.1 summarizes the  $g_m$  values for our SWCNT-network TFTs

| p    | $g_{\rm m}^{\rm f}$ (nS) by ${\rm DC}^{\rm a}$ | $g_{\rm m}^{\rm r}$ (nS)<br>by DC <sup>a</sup> | g <sub>m</sub> (nS)<br>by CP <sup>a</sup> | g <sub>m</sub> (nS)<br>by CP | g <sub>m</sub> (nS)<br>by AP |

|------|------------------------------------------------|------------------------------------------------|-------------------------------------------|------------------------------|------------------------------|

| 5.4  | 0.38                                           | 0.20                                           | 0.21                                      | 0.36                         | 0.33                         |

| 6.5  | 1.95                                           | 0.96                                           | 1.08                                      | 1.85                         | 1.50                         |

| 9.9  | 27.7                                           | 13.6                                           | 16.2                                      | 24.8                         | 20.3                         |

| 16.4 | 64.3                                           | 28.5                                           | 35.2                                      | 57.5                         | 50.3                         |

| 20.3 | 120                                            | 74.5                                           | 80.5                                      | 108.0                        | 113                          |

TABLE 3.1 g<sub>m</sub> values for SWCNT network TFTs with different p

$<sup>{}^{</sup>a}g_{m}{}^{f}$  and  $g_{m}{}^{r}$  is extracted from the TC curves with  $V_{g}^{max}$ =30 V in DC and CP modes, respectively.

with different p, extracted using the TC curves obtained in DC, CP and AP modes. With DC method, it can be found that  $g_m$  values vary by a factor of 2-3 when  $V_g$  is swept forwardly and reversely. This large discrepancy can lead to erroneous interpretations. With reference to the AP results, the forward DC sweep results in an overestimate of  $g_m$  ( $\mu$ ) while the the reverse one gives rise to an underestimate. When CP method was employed where a much smaller  $\Delta V_H$  was obtained, it was expected that the discrepancy would be much smaller. But in TABLE 3.1, it is found that the variation of  $g_m$  is only slightly smaller compared with that obtained from DC method, confirming the great importance of hysteresis-free TCs in  $\mu$  extraction. The adoption of AP method has resulted in hysteresis-free TCs, and thus consistent  $g_m$  values. Therefore, the  $g_m$  values extracted by the AP method is considered representative of the intrinsic device property, which is the starting point for a reliable determination of  $\mu$ .

#### 3.4.2 Dependence of $\mu$ on $C_{\rm g}$

Since  $\mu$  is inversely proportional to  $C_g$ , the determination of  $C_g$  is one of the most important steps for extraction of  $\mu$ . For the SWCNT-network TFTs, the majority of the publications use  $C_g$  values calculated from either  $C_P$  or the more rigorous cylindrical model presented by equation (3.1). Obviously, utilization of  $C_P$  underestimates  $\mu$  by the ratio  $C_P/C_g$ . For the calculated  $C_g$  according to equation (3.1),  $\mu$  can be either underestimated or overestimated due to the lack of accuracy in determining percolation geometrical parameters. In contrast,  $C_g$  through a direct  $C_P/C_g$  measurement can be straightforwardly utilized in the extraction owing to its accuracy.

It is expected from Fig. 3.7 that, for the low-density networks where  $C_g/C_P$  is small,  $\mu$  is severely underestimated by  $C_P$ . When p increases,  $C_g/C_P$  approaches 1 and the use of  $C_P$  for  $\mu$  extraction is a proper approximation. This is an important advance towards an accurate extraction of  $\mu$  for the SWCNT-network TFTs.

#### 3.4.3 Dependence of $\mu$ on current scaling behavior

In Si-MOSFETs,  $I_d \approx 1/L$ . By considering the percolation geometry of the nanotube networks, a more universal model presented by equations (2.3)-(2.5) has been proposed as discussed in Section 2.3. According to this model,  $\mu$  can be represented by,

$$\mu = \frac{1}{\frac{W}{L_{.t}} \left(\frac{L_{\rm nt}}{L}\right)^m} \frac{g_{\rm m}}{C_{\rm g} V_{\rm d}}$$

(3.2)