IT Licentiate theses 2015-001

# Techniques for Finite Element Methods on Modern Processors

KARL LJUNGKVIST

UPPSALA UNIVERSITY

Department of Information Technology

### Techniques for Finite Element Methods on Modern Processors

Karl Ljungkvist karl ljungkvist@it.uu.se

January 2015

Division of Scientific Computing

Department of Information Technology

Uppsala University

Box 337

SE-751 05 Uppsala

Sweden

http://www.it.uu.se/

Dissertation for the degree of Licentiate of Philosophy in Scientific Computing

© Karl Ljungkvist 2015 ISSN 1404-5117

Printed by the Department of Information Technology, Uppsala University, Sweden

#### Abstract

In this thesis, methods for efficient utilization of modern computer hardware for numerical simulation are considered. In particular, we study techniques for speeding up the execution of finite-element methods.

One of the greatest challenges in finite-element computation is how to efficiently perform the the system matrix assembly efficiently in parallel, due to its complicated memory access pattern. The main difficulty lies in the fact that many entries of the matrix are being updated concurrently by several parallel threads. We consider transactional memory, an exotic hardware feature for concurrent update of shared variables, and conduct benchmarks on a prototype processor supporting it. Our experiments show that transactions can both simplify programming and provide good performance for concurrent updates of floating point data.

Furthermore, we study a matrix-free approach to finite-element computation which avoids the matrix assembly. Motivated by its computational properties, we implement the matrix-free method for execution on graphics processors, using either atomic updates or a mesh coloring approach to handle the concurrent updates. A performance study shows that on the GPU, the matrix-free method is faster than a matrix-based implementation for many element types, and allows for solution of considerably larger problems. This suggests that the matrix-free method can speed up execution of large realistic simulations.

# Acknowledgments

First of all, I would like to thank my main advisor Jarmo Rantakokko for your help, advice and encouragement. Secondly, I thank my two co-advisors, Gunilla Kreiss and Sverker Holmgren, for your valuable experience and contacts, and for providing a broader picture. I also thank my co-authors Martin Tillenius, David Black-Schaffer, Martin Karlsson, and Elisabeth Larsson for collaboration. Furthermore, I am grateful for my colleagues and friends at TDB for providing a friendly atmosphere and making it a pleasure to go to work.

The work that resulted in Paper I was supported by the Swedish Research Council and carried out within the Linnaeus center of excellence UPMARC, Uppsala Programming for Multicore Architectures Research Center. The experiments in Paper II were conducted on computer systems provided by UPMARC. Finally, the travel grants received from Ångpanneföreningens Forskningsstiftelse and Anna-Maria Lundins stipendiefond are gratefully acknowledged.

# List of Papers

This thesis is based on the following two papers referred to as Paper I and Paper II.

I K. Ljungkvist, M. Tillenius, D. Black-Schaffer, S. Holmgren, M. Karlsson, and E. Larsson. Using Hardware Transactional Memory for High-Performance Computing. In *Parallel and Distributed Processing Workshops and Phd Forum (IPDPSW)*, 2011 IEEE International Symposium on , pages 1660-1667, May 2011.

**Contribution:** Development and experiments were conducted in close collaboration with the second author. The manuscript was written by the first two authors in collaboration with the remaining authors.

II K. Ljungkvist. Matrix-Free Finite-Element Operator Application on Graphics Processing Units. In Euro-Par 2014: Parallel Processing Workshops, volume 8806 of Lecture Notes in Computer Science, pages 450-461. Springer International Publishing, 2014.

Contribution: The author of this thesis is the sole author of this paper.

# Contents

| 1 | Inti | oduction                           | 1  |

|---|------|------------------------------------|----|

|   | 1.1  | Setting                            | 1  |

|   | 1.2  | Disposition                        | 2  |

| 2 | Fin  | te Element Methods                 | 3  |

|   | 2.1  | Background                         | 3  |

|   | 2.2  | The Matrix Assembly                | 5  |

|   |      | 2.2.1 Parallelization              | 6  |

|   | 2.3  | A Matrix-Free Approach             | 6  |

|   |      | 2.3.1 Evaluation of Local Operator | 8  |

|   |      | 2.3.2 Mesh Coloring                | 9  |

|   |      |                                    | 11 |

| 3 | Mo   | dern Processors                    | .5 |

|   | 3.1  | Background                         | 15 |

|   | 3.2  | =                                  | 5  |

|   | 3.3  |                                    | ١7 |

|   |      |                                    | 8  |

|   |      |                                    | 8  |

|   |      |                                    | 21 |

|   |      |                                    | 24 |

|   | 3.4  |                                    | 27 |

|   | 3.5  |                                    | 28 |

|   |      | -                                  | 31 |

|   |      |                                    | 32 |

| 4 | Out  | look 4                             | 11 |

|   | 4.1  | Ongoing and Future Work            | 11 |

# Chapter 1

# Introduction

## 1.1 Setting

When solving partial differential equations using the finite element method, the standard procedure consists of two distinct steps, a) an Assembly Phase, where a system matrix and right hand side vector are created to form a linear system, and b) a Solve Phase, where the linear system is solved. In most problems, most of the time is spent solving the linear system, and therefore, parallelization of the Solve Phase is a well studied problem, and derives on existing methods for parallel solution of sparse linear systems. On the other hand, the Assembly Phase is a more difficult task involving unstructured data dependencies.

However, with efficient parallelizations of Solve Phase in place, it becomes increasingly important to speed up also the Assembly Phase. This is also important for problems where the Assembly Phase needs to be performed repeatedly throughout the simulation, such as non-linear problems problems with time-dependent data.

A very related problem shows up when using the finite-element method with a matrix-free approach, where the Assembly Phase is merged into the sparse matrix-vector product inside linear solver, thus getting rid of the explicit system matrix. Since the resulting Operator Application operation is performed with a high frequency throughout the simulation, efficient implementation of this operation is crucial.

This matrix-free approach is motivated by the limited memory available for the system matrix, but also by recent trends in processor design where memory bandwidth is becoming the main bottleneck. The Operator Application is essentially equivalent to the assembly, so techniques for parallelization and optimization of the assembly are largely applicable also to the Operator Application.

One of the fundamental difficulties when performing the matrix assembly or matrix-free operator application, is the concurrent update of shared variables. Both these operations are computed as sums of contributions from all elements in the finite-element mesh, where the contributions from a single element correspond to degrees-of-freedom residing within that element, and they are typically parallelized by computing the sum and the contributions in parallel. Since many degrees-of-freedom are shared between multiple elements, many destination variables will be affected by multiple concurrent updates from different elements. This poses the challenge to avoid race conditions and maintain correctness.

This thesis concerns the efficient implementation of the matrix assembly and matrix-free operator application on modern parallel processors.

### 1.2 Disposition

In Chapter 2, the finite-element method is introduced, including the matrix-free version. In Chapter 3, recent trends in processor hardware are discussed; in particular, graphics processors and hardware transactional memory. In this context, the main contributions of the two papers are also presented. Finally, in Chapter 4, a overview of further ongoing and future work is found.

# Chapter 2

# Finite Element Methods

## 2.1 Background

The finite-element method (FEM) is a popular numerical method for problems with complicated geometries, or where flexibility with respect to adaptive mesh refinement is of importance. It finds applications in, e.g., structural mechanics, fluid mechanics, and electromagnetics [1]. Rather than solving the strong form of a partial differential equation, the finite element method is finds approximations of solutions to the variational, or weak, formulation. Consider the example of a Poisson model problem,

$$\begin{cases} \nabla^2 u = f & \text{on } \Omega, \\ u = 0 & \text{on } \partial\Omega. \end{cases}$$

The corresponding weak formulation is obtained by multiplying by a test function v in a function space  $\mathcal{V}$ , and integrating by parts, obtaining

$$(\nabla u, \nabla v) = (f, v) \ \forall v \in \mathcal{V}.$$

From this, the Finite Element Method is obtained by replacing the space  $\mathcal{V}$  with a finite-dimensional counterpart  $\mathcal{V}_h$ . This is typically done by discretizing the domain  $\Omega$  into a partitioning  $\mathcal{K}$  of elements.  $\mathcal{V}_h$  is then usually chosen to be the space of all continuous continuous functions which are polynomial within each element. There are different types of finite elements but the most popular ones include simplices (triangles, tetrahedra, etc.), as in Paper I, and quadrilaterals/hexahedrons, as in Paper II. For the case of triangle elements and their higher-dimensional generalizations, one typically considers functions polynomial of order p, referred to as  $\mathcal{P}^p$ . For quadrilateral elements, one instead usually considers functions polynomial of order p in each coordinate direction, e.g., bilinear for p = 1 or biquadratic for p = 2 in 2D. These

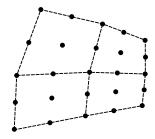

Figure 2.1: Location of the node points for second-order quadrilateral elements in 2D ( $Q^2$ ).

elements are referred to as  $Q^p$ . In the remained of this introduction, we assume  $Q^p$  elements, but  $\mathcal{P}^p$  are treated in a similar fashion.

To fix a unique such polynomial within an element, we need to determine its values at  $(p+1)^D$  node points (see Figure 2.1). Introducing basis functions  $\{\varphi_i\}$  in  $\mathcal{V}_h$ , which are zero at all node points except the *i*'th where it equals one, we can expand the solution u in this basis, and use the fact that we may replace v with  $\varphi_i$  since they constitute a basis in  $V_h$ . We then arrive at the following discrete system

$$\sum_{i=1}^{N} (\nabla \varphi_j, \nabla \varphi_i) u_i = (f, \phi_j) \ j = 1 \dots N$$

or, in matrix notation,

$$A\mathbf{u} = \mathbf{f},\tag{2.1}$$

where

$$A_{ij} = (\nabla \varphi_j, \nabla \varphi_i), \mathbf{f}_j = (f, \phi_j)$$

which has to be solved for the unknowns  $u_j$ , also referred to as degrees-of-freedom (DoFs). For a more complicated problem, e.g., involving time-dependence or non-linearities, a similar system will have to be solved in a time-stepping iteration or Newton iteration.

In summary, the computational algorithm for finding the finite-element solution consists of the following two phases:

- 1. Assembly phase

- 2. Solve phase

In the first phase, the system matrix A and the right-hand side vector  $\mathbf{f}$  are constructed. The second phase consists of solving the system in (2.1). In most applications, the solve phase is the most time consuming of the two. Therefore, speeding it up has been the target of much research. Since the matrix is, in

general, very large and very sparse, iterative Krylov-subspace methods are typically used for the solution. Within such iterative methods, most of the work is spent performing matrix-vector multiplications [2]. Parallelizations of the solve phase thus relies on efficient parallelization of the matrix-vector product for sparse matrices, which is a well studied problem. On the other hand, the assembly phase, which is a conceptually more complicated problem involving data dependencies and updating of shared variables, has only recently been attacked.

### 2.2 The Matrix Assembly

For the example of a stiffness matrix, the assembly consist of the following computation,

$$A_{ij} = (\nabla \varphi_i, \nabla \varphi_j) = \int_{\Omega} \nabla \varphi_i \cdot \nabla \varphi_j d\mathbf{x}.$$

Now the integral is split into a sum over all the elements in the mesh K,

$$A_{ij} = \sum_{k \in \mathcal{K}} \int_{\Omega_k} \nabla \varphi_i \cdot \nabla \varphi_j d\mathbf{x}. \qquad (2.2)$$

Since each basis function  $\varphi_i$  is non-zero only at the *i*'th DoF and zero on all others, it will only be non-zero on elements to which the *i*'th DoF belong. This effectively eliminates all but a few combinations of basis functions from each integral in the sum, i.e., the matrices in the sum are very sparse. If we introduce a local numbering of the DoFs within an element, there will be an element-dependent mapping  $I^k$  translating local index *j* to global index  $I^k(j)$ , and an associated permutation matrix  $(P_k)_{i,j} = \delta_{i,I^k(j)}$ . Using this, and introducing  $\varphi_l^k = \varphi_{I^k(l)}$  as the *l*'th basis function on element *k*, we can write (2.2) on matrix form as

$$A = \sum_{k \in \mathcal{K}} P_k a^k P_k^T \,, \tag{2.3}$$

where the local matrix  $a^k$  is defined as

$$a_{l,m}^{k} = \int_{\Omega_{k}} \nabla \varphi_{l}^{k} \cdot \nabla \varphi_{m}^{k} d\mathbf{x}. \qquad (2.4)$$

To summarize, the assembly consists of computing all of the local matrices  $a^k$ , and summing them up. The effect of the multiplication with the permutation matrices is merely that of distributing the element of the small and dense matrix  $a^k$  into the appropriate locations in the large and sparse matrix A.

#### 2.2.1 Parallelization

The standard way of parallelizing the assembly is to have multiple parallel threads compute different terms in the sum of (2.3). Since each of the local matrices are independent of each other, they can readily be computed in parallel. However, when the contributions are distributed onto the result matrix A, great care must be taken to ensure correct results.

As can be seen in Figure 2.1, a given degree of freedom is in general shared between multiple elements. This means that multiple contributions in the sum in (2.3) will update the same memory location. It is thus of great importance to perform the updates in a way such that race conditions are avoided (see Section 3.2). In Paper I, we avoid the race conditions by using various primitives for safe update of variables, chiefly transactional memory but also locks and atomic intrinsics. In Paper II, in addition to atomic intrinsics, we also utilize a mesh coloring approach where we can process the elements in groups such that no race conditions arise (see Section 2.3.2)

Alternative approaches for the parallelization have also been suggested, such as a node- or row-based parallelization where each thread is responsible for computing a single entry or row in the matrix [3, 4]. This removes the concurrent updates of shared variables, but instead introduces a lot of extra computations, as the local-element matrix has to be recomputed for each matrix entry it contributes to.

## 2.3 A Matrix-Free Approach

There are several problems with the two-phase approach considered in Section 2.1. First of all, as the degree of the finite elements is increased, the system matrix gets increasingly large and less sparse, especially for problems in 3D. In these cases, the system matrix A may simply be too large to fit in the memory of the computer.

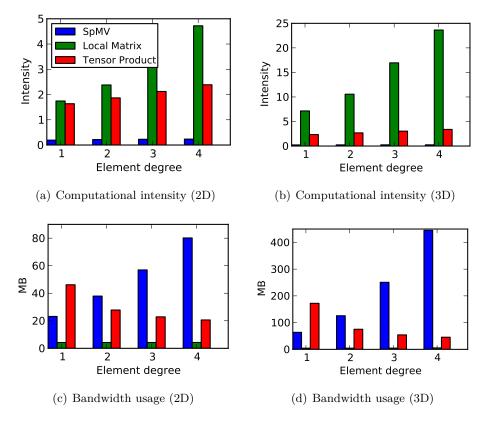

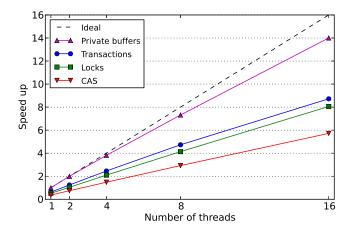

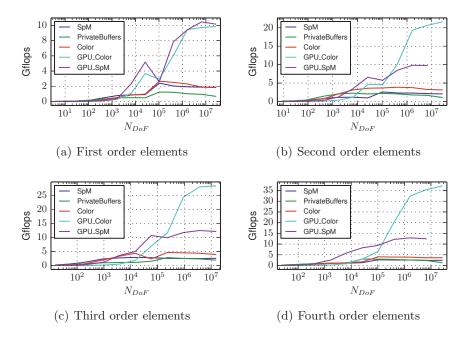

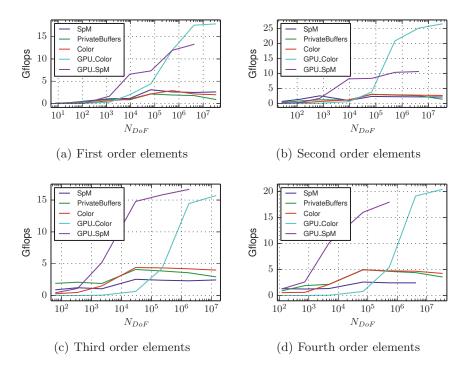

Secondly, the sparse matrix-vector multiplications (SpMV) constituting the bulk of work in the solve phase are poorly suited for execution on modern processors, since the number of arithmetic operations per memory access is low, making them bound by memory bandwidth rather than compute power [5, Chapter 7]. As can be seen in Figure 2.3, the *computational intensity*, defined as the number of arithmetic operations divided by the number of bytes accessed, is about 0.2, which is more than an order of magnitude lower than what is required for the most recent processors (see Section 3.4). Note that the SpMV operation has a very irregular access pattern for general matrices which reduces the utilization of the available bandwidth, requiring an even higher number of arithmetic operations per memory access.

Finally, when solving non-linear problems or problems with time-dependent coefficients, it might be necessary to reassemble the system matrix frequently throughout the simulation. This changes the relative work size of the assembly phase, and precomputing the large system matrix for only a few matrix-vector products may not be efficient. Similarly, when using adaptive mesh refinement, the matrix has to be reassembled each time the mesh is changed.

Motivated by this, several authors have suggested a matrix-free finite-element method. The idea builds on the observation that, to solve the system using an iterative method, the system matrix A is never needed explicitly, only its effect as an operator  $\mathcal{A}[\,\cdot\,]$  on a vector v. This means that if we can find a recipe  $\mathcal{A}[v]$  for how to form Av without having access to an explicit A, we can use  $\mathcal{A}[v]$  in the linear solver, just as we would have used Av.

Matrix-free methods have been used for a long time in computational physics in the form of Jacobian-Free Newton-Krylov methods to solve non-linear PDEs. There, by approximating the Jacobian-vector product Jv directly, one avoids having to explicitly form the Jacobian J of a Newton iteration for solving non linear problems, reducing space and computation requirements within the iterative linear solver [6].

The Spectral Element Method is a popular choice for hyperbolic problems with smooth solutions, which essentially is a finite-element method with very high-order elements; up to order ten in many cases [7]. Because of this, one can get the flexibility of finite-element methods combined with the rapid convergence of spectral methods. The latter are generalizations of the Fourier method, and converge at an exponential rate, in contrast to finite-difference methods or finite-element methods which only converge at an arithmetic rate [8]. Because of the hyperbolic nature of the PDEs involved, they can be integrated explicitly in time, and no linear system has to be solved during the simulation. Still, one needs to apply a FEM-type differential operator to the solution once to march forward in time, making a matrix-free approach interesting. Also, due to the typically very high number of degrees-of-freedom per element in spectral-element methods, the resulting matrix has a very low sparsity, which further motivates that a matrix-free technique can be beneficial. Usually, it is then based on the tensor-product approach described in Section 2.3.3.

Melenk et al. investigate efficient techniques for assembly of the spectralelement stiffness matrix, based on a tensor-product approach [9], In [10], Cantwell et al. compare matrix-free techniques based on a local matrix and tensor-product evaluation, with the standard sparse-matrix approach, and find that the optimal approach depends on both the problem setup and the computer system.

Kronbichler and Kormann describe a general framework implementing

tensor-based operator application parallelized using a combination of MPI for inter-node communication, multicore threading using Intel Threading Building Blocks, and SIMD vector intrinsics [11]. The framework has been included in the open-source finite-element framework deal.II [12, 13].

We form the matrix-free operator by using the definition of A from (2.3),

$$\mathcal{A}[v] = Av = \left(\sum_{k \in \mathcal{K}} P_k a^k P_k^T\right) v = \sum_{k \in \mathcal{K}} \left(P_k a^k P_k^T v\right).$$

In other words, we have simply changed the order of the summation and multiplication. Once again, the  $P_k$  simply permutation matrices which simply picks out the correct DoFs and distributes them back, respectively. In summary, the algorithm consists of (a) reading the local degrees of freedom  $v_k$  from the global vector v, (b) performing the local multiplication, and (c) summing the resulting vector  $u_k$  into the correct positions in the global result vector u,

(a)

$$v_k = P_k^T v$$

(b)  $u_k = a^k v_k$

(c)  $u = \sum_{k \in \mathcal{K}} P_k u_k$  (2.5)

This is essentially a large number of small and dense matrix-vector products which lends itself well to parallelization on throughput-oriented processors such as GPUs. Due to the similarity of this operation with the assembly, the same parallelization approach can be used, where we evaluate the local products in parallel. Also, for handling the concurrent updates of shared variables, in this case the DoFs, the same techniques can be used (see Section 3.5.2).

#### 2.3.1 Evaluation of Local Operator

Although the matrix-free operation as defined in (2.5) is a collection of dense operations, and thus significant improvement over the initial sparse matrix-vector product, the actual computational properties will depend on the evaluation of the local matrix-vector product, i.e, operation (b). To evaluate the integral in the definition of the local matrix, see (2.4), a mapping  $\mathbf{x} = f_k(\boldsymbol{\xi})$  from a reference unit element  $\hat{\square}$  to element k is used. Using this transformation, (2.4) can be rewritten as

$$a_{ij}^{k} = \int_{\hat{\sqcap}} \left( J_{k}^{-1} \hat{\nabla} \hat{\varphi}_{i} \right) \cdot \left( J_{k}^{-1} \hat{\nabla} \hat{\varphi}_{j} \right) |J_{k}| d\boldsymbol{\xi}, \qquad (2.6)$$

where  $J_k$  is the Jacobian of the transformation  $f_k$ , and  $\hat{\nabla}\hat{\varphi}_i(\boldsymbol{\xi})$  is the reference element gradient of reference element basis function  $\hat{\varphi}_i$ . In practice, this

integral is evaluated using numerical quadrature,

$$a_{ij}^{k} = \sum_{q=1}^{N_q} \left( J_k^{-1}(\xi_q) \hat{\nabla} \hat{\varphi}_i(\xi_q) \right) \cdot \left( J_k^{-1}(\xi_q) \hat{\nabla} \hat{\varphi}_j(\xi_q) \right) |J_k(\xi_q)| w_q, \qquad (2.7)$$

where  $\xi_q$  and  $w_q$  are the  $N_q$  quadrature points and weights, respectively. Typically, Gaussian quadrature is used since polynomials of arbitrary degree can be integrated exactly, provided enough points are used.

Now, if the mesh is uniform, i.e., if all elements have the same shape, then the Jacobian will be independent of k, and all the  $a^k$  will be equal. In this case, we can precompute a single local matrix a, which can be read by all the threads during the multiplication. In this case, a very favorable computational intensity can be achieved (see Figure 2.3).

For a general mesh, this cannot be assumed, and precomputing and storing the individual local matrices yields much too much data to be efficient. In this case, a tensor-product approach can be used to decrease the data usage, and increase the computational intensity (see Section 2.3.3). This is also the case for non-linear problems, even for a uniform mesh, since the  $a^k$  depend on the solution on element k.

In Paper II, we study the performance of the matrix-free approach in the case of a constant local matrix. Although this is restricted to linear problems on uniform meshes, it is still interesting to consider since in many cases, a uniform mesh can be used for large parts of the computational domain. The experiments and results are discussed in detail in Section 3.5.2.

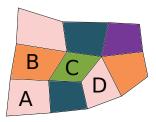

### 2.3.2 Mesh Coloring

In addition to the approaches for handling concurrent updates presented in Sections 3.2 and 3.3, we have also looked at a technique based on mesh coloring. This idea uses the fact that collisions can only appear between very specific combinations of elements, namely the ones sharing a degree-of-freedom. Thus, if we can process the elements in a way such that these specific combinations are never run concurrently, we can avoid the race conditions altogether. Looking at Figure 2.1, we note that only elements sharing a vertex will share DoFs with each other. Therefore, we would like to find a partitioning of the elements into groups, or *colors*, such that no two elements within a given color share a vertex. We could then process the elements a single color at a time, and prevent all conflicts from appearing.

Since we do not process all elements at once, the parallelism is reduced by a factor  $\frac{1}{N_c}$  where  $N_c$  is the number of colors. In general,  $N_c$  will be equal to the maximum degree of the vertex graph, which is defined as the number of elements sharing a vertex. For logically Cartesian meshes,  $N_c = 2^d$ ,

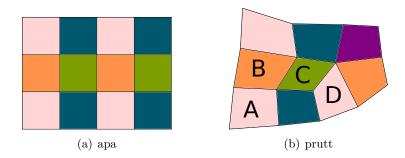

since all interior vertices are shared by the same number of elements;  $2^d$ , where d is the dimensionality of the problem. On the other hand, for more general meshes,  $N_c$  will be larger. Still, in both cases  $N_c$  is limited and independent of the size of the mesh, and the overhead will not grow with mesh refinement. Therefore, for large enough problems, the overhead will be small. The situation is illustrated in Figures 2.2 (a) and (b).

Figure 2.2: Coloring of (a) a uniformly Cartesian mesh, and (b) a more general mesh. For (b), note that A and B share a vertex and are thus given different colors, as are A and C. Since A and D do not share any vertices, they can be given the same color.

For a general mesh, finding the coloring can be done using various graph coloring algorithms [14, 15, 16]. In Paper II, where we use a uniform logically Cartesian mesh, handing out the colors is trivial. We assign colors by computing a binary number based on the index coordinates of an element. In 3D, the formula for the color  $c \in \{0, 1, \ldots, 2^d - 1\}$  is

$$c = (i_x \mod 2) + 2 \cdot (i_y \mod 2) + 4 \cdot (i_z \mod 2),$$

where  $i_x$ ,  $i_y$ , and  $i_z$  are the index coordinates of the element in the x, y, and z directions, respectively.

We note that, while the reduction of parallelism is low, this approach still introduces some superficial dependencies, since not all elements of different color will conflict with each other (e.g. elements from different corners of the domain). In particular, this introduces a global barrier between the processing of one color and the next one, preventing overlapping of elements although conflict free ones could be found. Resolving this situation completely is a difficult problem, but one way to solve it is to consider the dependency graph of the problem, which can be achieved using a task-based parallelization framework. One such task library is SuperGlue, which can handle complex dependencies, including atomicity [17, 18]. This type of dependency can be used to express the situation described in Section 3.2, namely that two operations can be performed in any order, but not concurrently. In [18],

Tillenius applies SuperGlue and achieves very good scaling for an N-body problem similar to the one considered in Paper I (see Section 3.3.4)

#### 2.3.3 Tensor-Product Local Operator

When the local matrix is not the same for all elements in the mesh, then precomputing and storing the local matrices becomes impractical due to the high memory requirement, which even exceeds that of the sparse matrix. In this case, we can take another step in the same direction as the original matrix-free approach, and exploit the specific structure of the local matrix. Once again, we note that the local matrix  $a^k$  is never needed explicitly, only its effect upon multiplication with a local vector v,

$$u_i = \sum_{j=1}^{n_p} a_{ij} v_j \,,$$

where  $n_p$  is the number of local DoFs. Equation (2.7) lets us rewrite this operation in the following manner,

$$u_{i} = \sum_{q=1}^{n_{q}} \left( J^{-1}(\boldsymbol{\xi}_{q})^{T} \hat{\nabla} \hat{\varphi}_{i}(\boldsymbol{\xi}_{q}) \right) \cdot \left[ J^{-1}(\boldsymbol{\xi}_{q}) \sum_{j=1}^{n_{p}} \hat{\nabla} \hat{\varphi}_{j}(\boldsymbol{\xi}_{q}) v_{j} \right] |J(\boldsymbol{\xi}_{q})| w_{q}, \quad (2.8)$$

where the element index k has been dropped. The entity in brackets is simply the gradient of v evaluated on the q'th quadrature point. Defining,

$$\nabla v_q = J^{-1}(\boldsymbol{\xi}_q) \sum_{j=1}^{n_p} \hat{\nabla} \hat{\varphi}_j(\boldsymbol{\xi}_q) v_j, \qquad (2.9)$$

(2.8) can be written as

$$u_i = \sum_{q=1}^{n_q} \left( J^{-1}(\boldsymbol{\xi}_q) \hat{\nabla} \hat{\varphi}_i(\boldsymbol{\xi}_q) \right)^T \cdot \nabla v_q |J(\boldsymbol{\xi}_q)| w_q.$$

or

$$u_{i} = \sum_{q=1}^{n_{q}} \hat{\nabla} \hat{\varphi_{i}}^{T}(\boldsymbol{\xi_{q}}) J^{-T}(\boldsymbol{\xi_{q}}) \nabla v_{q} |J(\boldsymbol{\xi_{q}})| w_{q}.$$

(2.10)

Now, for the quadrilateral or hexahedral elements under consideration, the basis functions  $\hat{\varphi}_i$  can be expressed as tensor products of d one dimensional basis functions  $\psi_{\mu}$ . Assuming three dimensions, we get

$$\varphi_i(\boldsymbol{\xi}) = \psi_{\mu}(\xi_1)\psi_{\nu}(\xi_2)\psi_{\mu_d}(\xi_d),$$

where we have dropped the symbol  $\hat{}$  for reference element, and introduced the multi-index  $i = (\mu, \nu, \sigma)$ . For the basis function gradient, this implies

$$\nabla \varphi_i(\boldsymbol{\xi}) = \begin{pmatrix} \psi'_{\mu}(\xi_1)\psi_{\nu}(\xi_2)\psi_{\sigma}(\xi_3) \\ \psi_{\mu}(\xi_1)\psi'_{\nu}(\xi_2)\psi_{\sigma}(\xi_3) \\ \psi_{\mu}(\xi_1)\psi_{\nu}(\xi_2)\psi'_{\sigma}(\xi_3) \end{pmatrix}.$$

Likewise, the quadrature points  $\xi_q$  can be expressed as

$$\boldsymbol{\xi}_a = (\xi^{\alpha}, \xi^{\beta}, \xi^{\gamma}),$$

where  $\xi^{\alpha}$  are the one dimensional quadrature points, and  $q = (\alpha, \beta, \gamma)$  is a multi-index. Note that we consistently use subscripts  $\mu$ ,  $\nu$ ,  $\sigma$  to index in DoF space, and superscript  $\alpha$ ,  $\beta$ ,  $\gamma$  as index for quadrature points. Defining

$$\psi^{\alpha}_{\mu} = \psi_{\mu}(\xi^{\alpha}), \ \chi^{\alpha}_{\mu} = \psi'_{\mu}(\xi^{\alpha}),$$

and using the multi-index notation, we can can compute the solution at the quadrature points as

$$v^{\alpha\beta\gamma} = \sum_{\mu} \psi^{\alpha}_{\mu} \sum_{\nu} \psi^{\beta}_{\nu} \sum_{\sigma} \psi^{\gamma}_{\sigma} v_{\mu\nu\sigma} .$$

We can now rewrite (2.9) as

$$\nabla v^{\alpha\beta\gamma} = (J^{\alpha\beta\gamma})^{-1} \sum_{\mu} \begin{pmatrix} \chi^{\alpha}_{\mu} \\ \psi^{\alpha}_{\mu} \\ \psi^{\alpha}_{\mu} \end{pmatrix} \sum_{\nu} \begin{pmatrix} \psi^{\beta}_{\nu} \\ \chi^{\beta}_{\nu} \\ \psi^{\beta}_{\nu} \end{pmatrix} \sum_{\sigma} \begin{pmatrix} \psi^{\gamma}_{\sigma} \\ \psi^{\gamma}_{\sigma} \\ \chi^{\gamma}_{\sigma} \end{pmatrix} v_{\mu\nu\sigma} , \qquad (2.11)$$

where  $J^{\alpha\beta\gamma} = J(\boldsymbol{\xi}_q)$  and the vector products are to be understood as elementwise multiplication. Likewise, for the second step, the numerical integration in (2.10), we have

$$v_{\mu'\nu'\sigma'} = \sum_{\alpha} \begin{pmatrix} \chi_{\mu'}^{\alpha} \\ \psi_{\mu'}^{\alpha} \\ \psi_{\mu'}^{\alpha} \end{pmatrix} \sum_{\beta} \begin{pmatrix} \psi_{\nu'}^{\beta} \\ \chi_{\nu'}^{\beta} \\ \psi_{\nu'}^{\beta} \end{pmatrix} \sum_{\gamma} \begin{pmatrix} \psi_{\sigma'}^{\gamma} \\ \psi_{\sigma'}^{\gamma} \\ \chi_{\sigma'}^{\gamma} \end{pmatrix} \left( J^{\alpha\beta\gamma} \right)^{-T} \nabla v^{\alpha\beta\gamma} w^{\alpha\beta\gamma} |J^{\alpha\beta\gamma}| .$$

$$(2.12)$$

The two very similar operations (2.11) and (2.12) both consists of a series tensor contractions – essentially dense matrix-matrix products – and a couple of element-wise scalar and vector operations. It is thus an significant improvement over the initial sparse matrix-vector product when it comes to utilization computational intensity, making very attractive for execution on throughput-optimized processors such as GPUs. This can be seen in Figure 2.3, which shows the computational intensity and bandwidth usage of the three main operator application approaches considered in this thesis. It is clear that in the cases when the local matrix implementation cannot be used, the tensor-product technique is very attractive alternative, especially for elements of high complexity, i.e. high dimension and polynomial order.

Figure 2.3: Comparison of operator approaches with respect to bandwidth usage and computational intensity. The bandwidth is computed as the amount of data which has to be read for a single operator application.

## Chapter 3

# Modern Processors

### 3.1 Background

As widely known, computer processors undergo an extremely fast development. According to the empirical observation of Moore's law, the number of transistors in a chip grows exponentially with a doubling every two years [19]. However, since the early 2000s this does no longer translate directly into a corresponding increase in serial performance. At that point, it was no longer possible to make significant increases in the clock frequency, since voltage could no longer be scaled down with the transistor size due to power issues. This is usually referred to as the power wall, or breakdown of Dennard scaling [20]. Instead, the focus has shifted towards increasing parallelism within the processor in the form of multicore designs.

This change has increased the burden on the programmer since utilizing a parallel processor is more difficult than a serial one [5]. When writing a parallel program, the work must be split into smaller tasks that can be performed concurrently, and issues such as communication and synchronization must be addressed.

### 3.2 Techniques for Updating Shared Variables

One of the main problems when programming multicore processors is the coordination of memory access. In contrast to cluster computers where the memory is distributed over the nodes, a multicore processor has a single memory which is shared between the cores. The multicore processors are typically programmed using threads, which all have access to the complete shared memory. While flexible, this approach allows for subtle bugs called race conditions.

A race condition occurs when two threads concurrently manipulate the

same memory location, resulting in undefined results (see example in Table 3.1). It is up to the application programmer or library developer to

| $\boldsymbol{x}$ | Thread 1                                                         | Thread 2                 |

|------------------|------------------------------------------------------------------|--------------------------|

| 0                | $x_1 \leftarrow x$                                               |                          |

| 0                | $x_1 \leftarrow x \\ x_1 \leftarrow x_1 + 1 \\ x \leftarrow x_1$ | $x_2 \leftarrow x$       |

| 1                | $x \leftarrow x_1$                                               | $x_2 \leftarrow x_2 + 1$ |

| 1                |                                                                  | $x \leftarrow x_2$       |

Table 3.1: Two threads increment the same variable x concurrently, leading to the result x = 1 instead of the expected x = 2.

guarantee that no race conditions can appear, and this is one of the main difficulties when writing multithreaded programs.

The code segments that potentially might conflict with each other, or with other copies of itself, is referred to as *critical sections*. In order to avoid race conditions, the critical sections need to be executed *mutually exclusively*, i.e. only a single thread is allowed within a critical section simultaneously.

The most common technique for achieving exclusivity is to use *locks*, which are mutually exclusive data structures with two operations — lock, which obtains the lock, and unlock, which releases the lock. If the critical section is surrounded with a lock and an unlock operation, then only a single thread will be allowed to be in the critical section, since any other thread will not succeed with the lock operation until the first thread has completed the unlock operation following its critical section.

Another way of achieving mutual exclusivity is the concept of *atomicity*. If all the operations in the critical section are considered an indivisible entity, which can only appear to the memory as a whole, then it can be executed safely concurrently. For simple critical sections, e.g. an incrementation of a variable, the processor architecture may offer native atomic instructions.

Atomic instructions usually perform well because of the efficient implementation in hardware. However, they cannot be used for general critical section and are limited to the available atomic instructions available. Although simple atomic instructions such as *compare-and-swap* can be used to implement somewhat more complex atomic operations, this is still very limited since, typically, not more than a single memory location can be manipulated.

Locks on the other hand are completely general, but can lead to several performance related issues. A deadlock occurs when two or more threads are waiting for each other's locks. Lock convoying is when many threads are waiting for a lock while the thread holding the lock is context switched and prevented from progressing. Priority inversion happens when a low-priority thread holds the lock, preventing execution of threads of higher priority [21].

### 3.3 Hardware Transactional Memory

Another more recent technique which also uses atomicity to achieve mutual exclusion is transactional memory. Rather than surrounding the critical section by lock and unlock operations, all the instructions of the critical section are declared to constitute an atomic transaction. Then, when the transaction is executed, the transactional memory system monitors whether any conflicting operations have been performed during the transaction. If conflicts are detected, the transaction is aborted, i.e., all of its changes to the memory system are rolled back to the pre-transactional state. On the other, if no conflicts were detected, the transaction commits, i.e., its changes are made permanent in the memory system.

Since this approach assumes a successful execution, and only deals with conflicts if they appear, it can be regarded as an *optimistic* approach. This is in contrast to the locks-based technique, where we always perform the locking even if no actual conflicts occurred, thus being a more *pessimistic* approach. This can potentially lead to lower overheads for the cases when contention is low, i.e., when conflicts are rare.

Another great benefit with transactional memory is in the ease of use. To get good performance with locks, it is necessary to dissect the algorithm and identify fine-grained dependencies in order to get the most parallelism out of it, and the problems mentioned in the previous section. On the other hand, with transactions, one simply has to declare the whole critical section as a transaction, and then the system will find conflicts automatically with a high granularity (typically cache-line size). With a sufficiently efficient implementation of the transactional memory system, this has the potential to simplify the programming of high-performance parallel programs.

Transactional Memory was first introduced by Herlihy and Moss in 1993, where they suggest an implementation based on a modified cache-coherence protocol [21]. In the following years, several studies investigating possible transactional-memory implementations in hardware or software were published [22, 23, 24, 25]. Around 2008, Sun Microsystems announced the Rock processor; the first major processor intended for commercial use to feature transactional memory in hardware [26]. Although eventually canceled after the acquisition of Sun by Oracle, several prototype Rock chips were available to researchers. More recently, IBM has included transactional memory in the BlueGene/Q processor [27], whereas Intel has introduced transactional memory in the form of the Transactional Synchronization Extensions in their Haswell processor series [28]. For both of these systems, relatively good performance when applied to scientific computing has been demonstrated [29, 30].

#### 3.3.1 The Rock Processor

All the experiments in Paper I were performed a prototype version of the Rock processor. The Rock is a 16-core processor featuring the SPARC V9 instruction set. The cores are organized in four clusters of four cores, where each cluster shares a 512 kB L2 cache, a 32 kB instruction cache, two 32 kB L1 data caches, and two floating point units. Except for hardware transactional memory, other exotic features of the Rock processor includes Execute Ahead and Simultaneous Speculative Threading. Execute Ahead lets a single core continue performing future independent instructions in the case of a longlatency event, e.g., a cache miss or TLB miss, and return to the previous point once the lengthy operation is ready, performing a so called replay phase. In Simultaneous Speculative Threading, this is expanded even further where two cores can cooperate with performing the future independent instructions and the replay phase, thus executing a single serial instruction stream at two points simultaneously. In both of these cases, an additional benefit is that thread executing future instructions can encounter further cache misses, effectively acting as a memory prefetcher. Both EA and SST utilize the same checkpointing mechanism used to implement transactional memory [26].

The Rock supports transactional memory by adding two extra instructions:

- chkpt <fail\_pc>

- commit

The chkpt instruction starts a transaction, and the commit instructions ends it. If a transaction is aborted, execution jumps to the address referred to by the fail\_pc argument. A new register %cps can then be read to get information on the cause of the abort.

#### 3.3.2 Failed Transactions

The Rock processor implements a best-effort transactional memory system, meaning that any transaction may fail, whereas other, bounded, implementations provide guarantees that transactions satisfying certain size criteria always commit. A best-effort implementation offers flexibility and has the advantage of potentially committing transactions of much larger size than on a corresponding bounded implementation. However, since transactions always may fail, even if there are no conflicting writes, a clever fail handler is necessary to ensure forward progress and performance. In Table 3.2, the various reasons for a fail are listed, along with the associated bits of the **%cps** register. In the following, we discuss the most important reasons for failure and how we handle them, based on our hands-on experience and the

|   | ${f Bit}$                        | Meaning                             |

|---|----------------------------------|-------------------------------------|

|   | 0x001                            | Invalid                             |

|   | 0x002                            | Conflict                            |

|   | 0x004                            | Trap Instruction                    |

|   | 0x008                            | Unsupported Instruction             |

|   | 0x010                            | Precise Exception                   |

|   | 0x020                            | Asynchronous Interrupt              |

|   |                                  | 3.5                                 |

|   | ${f Bit}$                        | Meaning                             |

|   | 0x040                            | Size                                |

|   |                                  |                                     |

| - | 0x040                            | Size                                |

| - | 0x040<br>0x080                   | Size<br>Load                        |

|   | 0x040<br>0x080<br>0x100          | Size<br>Load<br>Store               |

| - | 0x040<br>0x080<br>0x100<br>0x200 | Size Load Store Mispredicted Branch |

Table 3.2: Reasons for a failed transaction as indicated by the bits of the **%cps** register. This information is based on a table in [31].

information in [32]. The absolute majority of the failed transactions belonged to one of the following types:

**Conflict** Another thread tried to modify the same memory address.

Load A value could not be read from memory.

Store A value could not be stored to memory.

Size The transaction was too large.

Due to limited hardware, there are many constraints on transactions, such as the total number of instructions, and the number of memory addresses touched. In our experiments, we were able to successfully update up to 8 double precision variables (64 bytes) in a single transaction. More updates frequently resulted in the transaction failing with the **Size** bit set. However, once again we note that the transactional memory still provides no guarantees, and also smaller transactions sometimes failed with the **Size** bit set. A transaction will be aborted with the **Conflict** bit set if another core made a conflicting access to the same cache line. The **Load** or Store **Store** bits are set when the transaction tries to access memory which is not immediately available, which happens in the case of a L1 cache miss or a TLB miss. In addition, the **Store** bit is set if the memory location is not exclusive in the cache coherency protocol.

For the transactions failing due to **Conflict**, we employ a backoff strategy in our fail handler, where we introduce a random but exponentially increasing delay before retrying the transaction. This is reasonable, since if two threads

accessed the same data recently, they are likely to do so again. If the transaction failed due to a **Store** error, we noticed that simply retrying it indefinitely often never led to a success. The problem is that, although the memory system notices that the data is not available or in the proper L1 cache state, and aborts the transaction, it does not fetch it and make it exclusive. To trigger this, we must write to the memory location outside of a transaction, while at the same time making sure not to change or corrupt the data. We achieve this by utilizing a trick from [32], in which we perform a dummy compare-and-swap – write zero if the memory location contains zero. After this, we retry the transaction. In the event of a **Load** error, we simply read the corresponding data outside of a transaction to have the memory system fetch it into the caches, and then retry the transaction. The fail handling scheme is summarized in Listing 3.1.

```

1

while transaction fails:

2

if cps == conflict:

3

back-off

4

else if cps == store:

5

compare-and-swap data

6

else if cps == load:

7

load data

8

retry transaction

```

Listing 3.1: Strategy for handling failed transactions

In Table 3.3, we see the amount of failed transactions for the different experiments conducted on the Rock processor.

| Experiment              | Failed Trans. | Conflict | Load   | Store |

|-------------------------|---------------|----------|--------|-------|

| Overhead (1 update)     | 0.00026 %     |          |        |       |

| Overhead (8 updates)    | 0.0004~%      |          |        |       |

| Contention (100 $\%$ )  | 13.2~%        |          |        |       |

| Contention $(0.098 \%)$ | 0.099~%       |          |        |       |

| FEM (few computations)  | 18.8 %        | 0.4~%    | 95.6~% | 4.0~% |

| FEM (many computations) | 19.2 %        | 0.2~%    | 96.7~% | 3.1~% |

| N-body                  | 0.4 %         | 51.9 %   | 34.0~% | 3.1~% |

Table 3.3: Amount of failed transactions as percentage of the total number of updates. Included is also statistics of the fail cause, except for the microbenchmarks, where the fail reason was not recorded to minimize overhead.

#### 3.3.3 Microbenchmarks

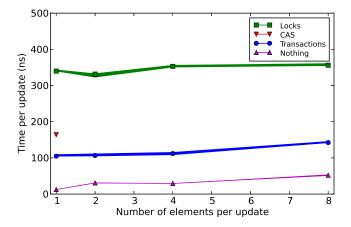

In order to investigate the performance of the transactional memory system for performing floating point updates, two microbenchmarks were devised, studying the overhead of transactions, and the sensitivity to contention, respectively. In all the experiments, we tried using two types of locks: Pthread mutex and Pthread spin lock. However, since the spin lock always performed the same or worse, we exclude it from the discussion.

#### Overhead of Synchronization

The point of the **overhead** microbenchmark is to see if transactions have lower overhead than the other synchronization techniques. In this program, we let a single thread perform one million increments of a small floating point array using protected updates. In addition to performing the update inside an atomic transaction, surrounding the update with a lock, and performing the update using the compare-and-swap instruction, we also include a reference version which does no protection at all, constituting base line. Since only a single thread is updating the array, overhead related to contention should not affect the result. To see if more updates can compensate for the overhead, we vary the size of the array from one to eight doubles. The compare-and-swap version is limited to a single double precision value and cannot be used for larger arrays if the whole array should be updated in a single atomic operation. Note that for cases where it is acceptable to ensure atomicity elementwise, the compare-and-swap technique would likely perform very poorly since the overhead is proportional to the number of updates. Finally, the Rock processor can only perform compare-and-swap on integer values, incurring some overhead in the form of conversion between floating point and integer numbers, which involve stores and loads.

In the version based on transactions, we do not utilize any fail strategy other than simply retrying the transaction if it failed. However, we do make sure that all the data is present in the cache before the experiment to avoid the problem with **Store** errors described in Section 3.3.2. To get information on the amount of failed transactions, we count both the number of started transactions, and the number of successful ones.

Since the operation we are trying to benchmark – the update of a few floating point variables – is very small, we have to be very careful during the implementation. For our first version, which was implemented in C, we observed that the compiler produced very different results for the different methods, yielding large performance differences. Therefore, we instead reimplemented all of the benchmarks in assembly code, which produced much more similar programs, and also improved the overall performance. Moreover, to further minimize the difference between the different methods,

we count the number of failures also for the methods where all updates will succeed.

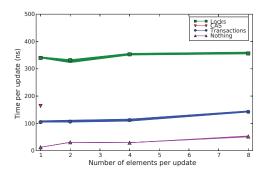

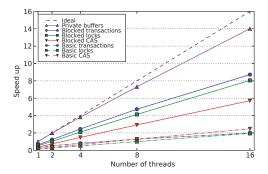

Figure 3.1: Result of the **overhead** benchmark. The width of the lines show the variation from 100 runs, measured as lower to upper quartile.

Looking at Figure 3.1, we see that the results confirmed our prediction that transactions have the lowest overhead. Although we observed a few spurious failed transactions – see Table 3.3, these do not affect the results and are neglected. We also see that, while limited to a single entry, the compare-and-swap version performed decently in that case.

#### **Effect of Contention**

In the **contention** microbenchmark, we want to see how the performance is affected if we add contention in the form of other threads trying to update the same memory location. We let one thread per core update its own entry in an array of length 16, and introduce contention by having threads 2-16 sometimes also write to the memory location of thread 1. It is not entirely straightforward how to go about to attain a desired level of conflicts, since although two threads write to the same location, a conflict might not actually happen. By controlling with what probability threads 2-16 write to the shared location, we can quantify percentage of potential conflicts. Although this is no perfect measure of the number of conflicts, the two will definitely be correlated, and at probability 100%, in which case all threads always update the same location, we will have the highest amount of contention possible. Furthermore, we avoid false sharing by making sure that array entries reside their own cache lines. The experiment consists of each thread performing one million updates each.

Here, we include three versions; using transactions, locks and compare-

and-swap, respectively. Since we expect quite a few conflicts, the version based on transactions includes the fail handling strategy in Listing 3.1. The compare-and-swap version employs a simplified strategy involving only the exponential backoff. To see what number of actual conflicts we obtain for a given contention probability, we maintain a counter of the number of transactions failing on the initial try. We also measure the number of conflicts for the locks case, which is achieved by first attempting to grab the lock using the pthread\_mutex\_trylock function, which gives us information on whether the lock was available on the first try or not. If there was a conflict, we simply retry grabbing the lock, but this time using the regular blocking pthread\_mutex\_lock.

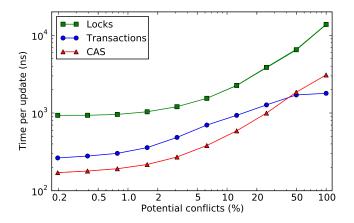

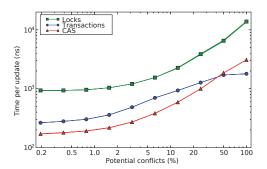

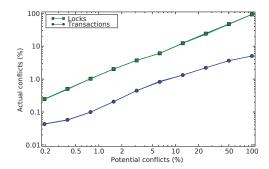

Figure 3.2: Results of the **contention** benchmark, presented as the median of 100 runs. The width of the lines show the variation from lower to upper quartile.

In Figure 3.2, we see that the version using locks once again performed the worst. What was more surprising was the results for transactions and compare-and-swap. We had expected transactions to have a low overhead when contention was low, and a high overhead when contention was high as many transactions would fail and have to be retried. Also, from the overhead experiment, we expected compare and swap to be slower than transactions due to the higher overhead, but possibly be less sensitive to contention. In contrast, the results show that compare-and-swap was faster than transactions for low contention, whereas transactions leveled off for high contention making it the fastest method in that case. One explanation for this can be that the store buffer serializes the writes, stopping more transactions than necessary from failing.

From Table 3.3, we conclude that there indeed was a clear correlation between potential and actual conflicts. However, we also see that even if 16 threads update a single location as frequently as possibility (the "100 %" case), only a fraction of the transactions actually fail. While we do use the exponential backoff, the initial attempts are in no way designed to avoid conflicts.

#### 3.3.4 FEM Assembly Experiment

In Paper I, the performance of the transactional memory system of the Rock processor for performing floating point updates is studied. We compare the performance of three different versions; one based on locks, one based on atomic operations using the compare-and-swap instruction, and one based on transactional memory.

Since transactional memory has the potential to simplify implementation of parallel algorithms, we consider a straight-forward assembly based on (2.3). For instance, this means that we store the matrix in a full format, since a sparse format would require knowledge of the sparsity pattern beforehand. Although this limits how large problems we can study, it should still let us get a rough estimate of the expected performance. While it does use much more bandwidth and introduce a lot of additional cache misses compared to a sparse matrix format, the memory pattern is still similar to what can be expected when assembling a much larger sparse matrix of the same size as our full matrix. Also, by storing the matrix elements more sparsely, we largely avoid false sharing.

To study how the performance is effected by the number of operations within the evaluation of the local matrix, we have considered two versions; one with only a few computations, and one with many computations. The actual computations are artificial in both cases. The second version represents more advanced methods, such as multi-scale finite-element methods, where a smaller finite-element problem is solved within each element [33].

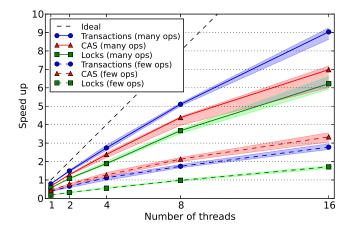

Figure 3.3 shows the results of the finite-element assembly application. We can see that the compare-and-swap implementation was fastest for the memory-intensive version with few operations, whereas for the compute-intensive version with many operations, transactions were the fastest. This confirms that transactions perform the best when contention is low. The locks version was the poorest overall. Also, we note the large statistical variation due to the rather short run times of this experiment. Finally, we observed a very low speedup for the memory-intensive version – 3.3x at best for the compare-and-swap implementation – which can be explained by the fact that the application is memory bound.

Considering the amount of aborted transactions (Table 3.3), we see that there was a relatively high amount of aborts – the highest of all experiments. However, looking at the distribution of causes, we see that there was in fact

Figure 3.3: Median speedup over serial for the different finite-element assembly approaches. The shaded areas show the variation from lower to upper quartile.

almost no conflicts. Rather, the vast majority of all the fails are caused by cache misses or other memory-related problems. This is not surprising as most of the variables are stored in their own cache line, and are only changed very rarely.

### N-Body Simulation

In Paper I, we also study a similar problem; an N-body simulation. This is a very common model in scientific applications, such as cosmology [34], molecular dynamics [35], and even machine learning [36]. In the N-body simulation, the forces acting between a number of particles have to be calculated. Since the force on a given particle consists of a sum of contributions from all other particles, it also involves concurrent updates of shared variables. Once again, we have only studied the simple all-to-all interaction. More advanced algorithms for N-body simulation include, e.g., Barnes-Hut [37], or the Fast Multipole Method [38].

Just as for the FEM application, we evaluate a locks-based version, one using compare-and-swap, and one based on transactions. To decrease the overhead, we consider chunks of particles and update a whole chunk using a single transaction or lock. This approach is not available for the compare-and-swap version, due to the limitation to a single variable. Finally, we include a more advanced algorithm using privatization of memory to avoid the conflicts altogether, at the price of more memory and more effort from the programmer.

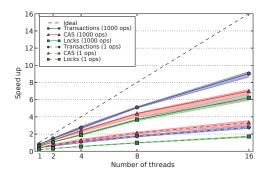

In Figure 3.4, we see the results of the N-body experiment, from which we

can conclude that transactions performed slightly better than locks. Compareand-swap performed considerably worse, probably because of the lack of blocking. However, we also see that the more advanced implementation based on privatization is still the superior version.

Figure 3.4: Results of the N-body experiment as speedup over the fastest serial version. The (negligible) width of the lines show the statistical variation from first to third quartile.

In this case, only 0.4~% of the transactions failed (see Table 3.3). The reason for this surprisingly low number is that the algorithm has a low memory footprint – only 900 cache lines compared to more than 21 000 cache lines for FEM application. In addition, this data is accessed in a fairly dense matter, due to the the chunking technique. This means that most of the memory accesses will hit in the cache. Out of the transactions that did fail, the majority were caused by conflicting writes. Note that for this application as much as 11~% of the failed transactions had an unknown cause.

#### Conclusion

Summarizing the results from both applications, we conclude that transactions were faster than both locks and compare-and-swap for updating shared floating-point variables, but that avoiding concurrent updates is the best choice when it is available. However, we also saw that for some applications, such as the compute-intensive matrix assembly, transactions can provide a moderate speed up also when a very naive algorithm is used. With the complicated fail handling strategy provided by a library, and with better compiler support for transaction programming, this certainly confirms that transactional memory can simplify parallel programming.

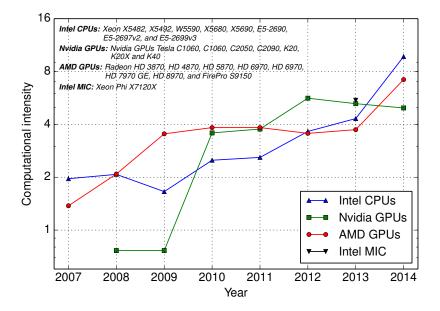

## 3.4 Computational Intensity Trends

In addition to the arrival of multicore processors, another problem which has become more severe recently is the fact that memory bandwidth has not scaled at the same rate as the processors. This situation was not changed by the transition to multicore processors; many slow cores will need as much memory bandwidth as a single fast one. Between 2007 and 2012, the processing power (Gflop/s) of Intel processors increased by about 30 % annually, whereas corresponding increase in the bandwidth (GB/s per socket) was only about 14 %. This balance between computations and bandwidth can be characterized by the *computational intensity*, which is defined as the ratio of the peak processing power in Gflop/s to the maximum bandwidth in GB/s. Looking at Figure 3.5, we see that recent multicore processors and GPUs have a double-precision computational intensity of about 5-10. This means that for each double-precision floating-point number (8 bytes) fetched from the memory, about 40-80 double-precision arithmetic operations are required.

Figure 3.5: Change in computational intensity for processors during the last six years for double precision operations. Graph based on a blog post by Karl Rupp [39].

We therefore have a situation where most of the 'performance improvement' of new processors will come in the form of additional computations per memory fetch. Only for applications with a high enough computational intensity will this translate to any actual performance improvement. For applications which are dominated by operations limited by bandwidth, e.g., sparse matrix-vector products, stencil computations, or FFT, we can not expect any speed up.

This means that, in order to continue speeding up our applications by leveraging new capacity, we have to find algorithms that better match upcoming processor architectures. In practice, this means algorithms which need less memory bandwidth, possibly at the price of requiring additional computations. Indeed, as computations become abundant, being wasteful and recomputing previous results might actually prove beneficial.

Next, we look at one of the main new trends in computer processors – graphics processors, and how the high-performance computing community has been taking advantage of them.

## 3.5 Graphics Processors

In recent years, programming of graphics processing Units (GPUs) for general computations have become very popular. Driven by the insatiable demand from the gaming market for ever more detailed graphics, the GPUs have evolved into highly parallel streaming processors capable of performing hundreds of billions of floating point operations per second.

The design of GPUs is streamlined to the nature of their workload. Computer graphics essentially consists of processing a very large number of independent polygon vertices and screen pixels. Because of the very large number of tasks, there is no problem with executing each individual task slow as long as the overall throughput is high. Therefore, most of the transistors of a GPU can be used for performing computations. This is in contrast to CPUs, which are expected to perform large indivisible tasks in serial, or a few moderately sized tasks in parallel, possibly with complicated inter-dependencies. To optimize for this workload, i.e. making a single task finish as quickly as possible, a considerable amount of the hardware of a CPU – in fact most of it – is dedicated to non-computation tasks such as cache, branch prediction and coherency. Also, to get the necessary data for all the individual work items, the memory system of graphics cards tend to be focused on high bandwidth, whereas the caching system of a CPU aims at achieving low latency. Finally, as computer graphics in many cases can tolerate a fairly low numerical precision, the GPU architecture has been optimized for single-precision operations. This means that while CPUs can typically perform operations in single precision twice as fast as in double precision, this factor is of the order of 3-8 for GPUs. As a consequence of the higher computing power per transistor, GPUs achieve a higher efficiency,

both economically (i.e. Gflops/\$) and power-wise (i.e. Gflops/W), although the most recent multicore CPUs are improving in this respect. See Table 3.4 for a comparison of different modern CPUs and GPUs.

| Processor            | Cores | Gflops         | GB/s | Gflops/W      | Gflops/\$       |

|----------------------|-------|----------------|------|---------------|-----------------|

| Intel Core i7 5960X  | 8     | 384 (768)      | 68   | 2.7(5.5)      | 0.38 (0.77)     |

| Intel Xeon E7-2890v2 | 15    | 336 (672)      | 85   | 2.2(4.3)      | 0.052(0.1)      |

| Intel Xeon E5-2699v3 | 18    | $662\ (1325)$  | 68   | 4.6(9.1)      | $0.16 \ (0.32)$ |

| Nvidia Tesla M2090   | 512   | $666 \ (1332)$ | 177  | 3.0 (5.9)     | 0.17(0.33)      |

| Nvidia Tesla K20X    | 2688  | 1310(3935)     | 250  | 5.6 (16.7)    | 0.34(1.0)       |

| Nvidia Tesla K40     | 2880  | 1429(4291)     | 288  | $6.1\ (18.3)$ | 0.26 (0.78)     |

| Nvidia Tesla K80     | 4992  | $1868\ (5611)$ | 480  | 6.2(18.7)     | 0.37(1.1)       |

| AMD FirePro S9150    | 2816  | $2534\ (5069)$ | 320  | 10.8 (21.6)   | 0.77(1.5)       |

| Intel Xeon Phi 7120P | 61    | 1208(2417)     | 352  | 4.0 (8.1)     | 0.29 (0.59)     |

Table 3.4: Comparison of various processing units. All numbers are peak values and taken from the manufacturers' specifications. The numbers in parentheses are for single precision, and the others are for double precision.

Scientific applications, such as e.g. stencil operations or matrix-matrix multiplications, are usually comprised of many small and similar tasks with a high computational intensity. Because of this, the fit for the throughputoptimized high-bandwidth GPU hardware has in many cases been great. However, several limitations of the graphics-tailored GPU architecture limit how well applications can take advantage of the available performance potential of GPUs. For instance, few applications possess the amount of parallelism needed to saturate the massively parallel GPUs. In addition, for most scientific applications, double precision is necessary to obtain meaningful results, which, as mentioned, has a performance penalty over single precision. Furthermore, while dependencies and synchronization are unavoidable parts of most algorithms, these are often very difficult or even impossible to resolve on GPUs. Thus, in order to fully utilize GPUs, it is often necessary to make substantial changes to existing algorithms, or even invent new ones, which take these limitations into account. Another issue is that data has to be moved to the graphics memory before it can be accessed by the GPU. which is presently done by transferring the data over the relatively slow PCI bus. To avoid this bottleneck, data is preferably kept at the GPU for the entire computation. Another approach is to hide the latency by overlapping computation and data transfer.

The history of general-purpose graphics-processing unit (GPGPU) computations started around 2000 when dedicated graphics cards were becoming mainstream. In the beginning, the general-purpose computations had to be shoehorned into the graphics programming pipeline by storing the data

as textures and putting the computations in the programmable vertex and pixel shaders. Examples of early successful general-purpose computations on graphics hardware are matrix-matrix multiplication [40], a solution of the compressible Navier-Stokes equations [41], and a multigrid solver [3]. A summary of early work in GPGPU can be found in the survey paper by Owens et al. [42].

However, the many restrictions and the fact that a programming model for graphics had to be exploited made it a daunting task to do general-purpose computations with the graphics pipeline. In response to this, at the end of 2006, Nvidia released CUDA, Compute Unified Device Architecture, which simplified the programming and led to a dramatic increase in interest for GPGPU.

The CUDA platform provides a unified model of the underlying hardware together with a C-based programming environment. The CUDA GPU, or device, comprises a number of Streaming Multiprocessors (SMs) which in turn are multi core processors capable of executing a large number of threads concurrently. The threads of the application are then grouped into blocks of threads and each block is executed on a single SM, independently of the other blocks. Within a thread block or an SM, there is a piece of shared memory. Furthermore, it is possible to have synchronization between the threads of a single block, but it is not possible to synchronize threads across blocks, except for a global barrier. There is also a small cache shared between the threads of a block.

An important feature of CUDA, and arguably the most crucial aspect to attain good utilization of the hardware, is the memory model. Because transfers from the main device memory are only made in chunks of a certain size, and due to poor caching capabilities, it is important to use all the data of the chunks which are fetched. When the threads within a block access a contiguous piece of memory simultaneously, such a *coalesced* memory access is achieved. For further details on the CUDA platform, see the CUDA C Programming Guide [43]. Examples of fields where CUDA has been successfully utilized include molecular dynamics simulations [44], fluid dynamics [45], wave propagation [46], sequence alignment [47] and, Monte Carlo simulations of ferromagnetic lattices [48].

In response to CUDA and the popularity of GPU programming, OpenCL was launched by the consortium Khronos Group in 2008 [49]. In many respects, such as the hardware model and the programming language, OpenCL and CUDA are very similar. However, in contrast to CUDA, which is proprietary and restricted to Nvidia GPUs, OpenCL is an open standard, and OpenCL code can be run on all hardware with an OpenCL implementation; today including Nvidia and AMD GPUs, and even Intel and AMD CPUs. While the same OpenCL code is portable across a wide range of platforms, it

is usually necessary to hand tune the code to achieve the best performance. In addition, CUDA, being made by Nvidia specifically for their GPUs, is still able to outperform OpenCL in comparisons and when optimal performance is desirable, CUDA is still the natural choice [50, 51].

Critique has been raised as to the long-term viability of techniques and codes developed for GPUs in general and CUDA in particular, since these are very specific concepts which might have a fairly limited life time. However, an important point is that GPUs are part of a larger movement – that of heterogeneity and increasing use of specialized hardware and accelerators. Recently, all the major processor vendors have started offering dedicated accelerators for computations, which, in addition to the Tesla GPUs of Nvidia, include Intel's Xeon Phi co-processor and the very recently announced FirePro cards by AMD (see Table 3.4). Since most of these accelerators share a similar throughput-oriented architecture, once an algorithm has been designed for one of them it is not very difficult to convert to the others. Therefore, developing algorithms and techniques for dedicated accelerators, such as GPUs, is relevant also for the technology of the future.

#### 3.5.1 Finite-Element Methods on GPUs

Due to the higher complexity of the assembly phase, early attempts at leveraging GPUs for finite-element computations focused on speeding up the solve phase [3, 52, 53, 54]. Since in matrix-based finite-element software, the solve phase is based on a general sparse matrix-vector product, these can readily take advantage of sparse linear algebra libraries for GPUs. Examples of such libraries include CUSPARSE, an Nvidia library for sparse computations included in CUDA since 2010 [55]; and PARALUTION, a library for sparse linear algebra targeting modern processors and accelerators including GPUs [56], available since 2012.

On the other hand, as explained in Section 2.2, the assembly is a much more complicated operation requiring explicit implementation to be performed on the GPU. In [4], Cecka et al. explore different techniques for performing the assembly on GPUs, using both element-wise and node-wise parallelization. Dziekonski et al. propose a GPU-based implementation of the assembly with computational electrodynamics in mind [57]. Markall et al. study what implementations of FEM assembly are appropriate for many-core processors such as GPUs compared to multi-core CPUs [58].

A number of studies have considered finite-element solution of hyperbolic problems on GPU, which often take on a matrix-free approach. However, we are not aware of existing matrix-free work for the GPU targeting elliptic and parabolic PDEs. In [16], Komatitsch et al. study a high-order spectral-element method applied to a seismic simulation on a single GPU. In

[59], the authors expand this to a cluster of GPUs using MPI. While using the spectral-element method, basically a high-order finite-element method, in the earthquake application considered, the partial differential equations are hyperbolic and an explicit time stepping can be used. Together with the Gauss-Lobatto-Legendre integration scheme, which yields a diagonal mass matrix, this means that no linear system is solved during the simulation, although the matrix-free operator application still constitute the most important operation.

Klöckner et al. investigate a GPU-parallelization of a discontinuous Galerkin (DG) method for hyperbolic conservation laws [60]. Due to properties of the DG method, the mass matrix is block diagonal, which means that the system can easily be solved element-wise, removing the need for an iterative solve phase.

### 3.5.2 Matrix-Free FEM Experiments

In Paper II, we study the performance of a GPU-based implementation of the matrix-free finite-element operator application described in Section 2.3, for future inclusion in a FEM solver of parabolic and elliptic PDEs. This is motivated by the improved computational intensity of this approach, which has the potential of letting us take advantage of immense the performance offered by the GPUs.

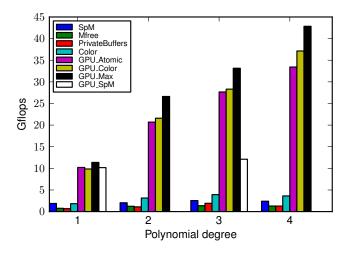

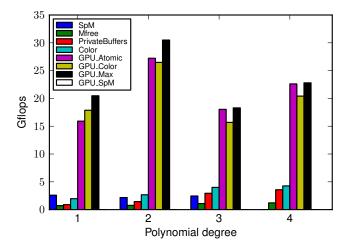

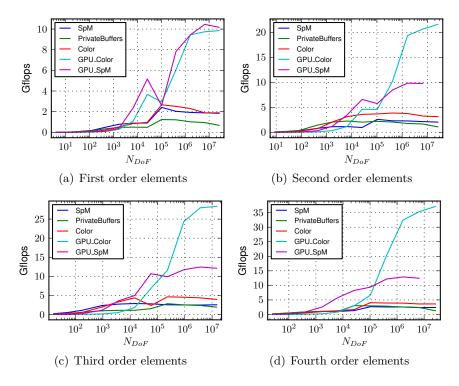

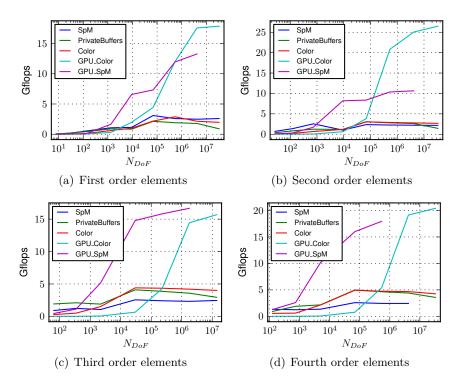

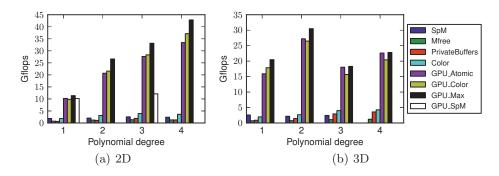

To do this, we apply the matrix-free method to a Poisson problem similar to the one in Section 2.1. We consider unit square or cube discretized by a uniform Cartesian mesh, and elements of polynomial order one to four, in 2D and 3D. While being a quite specific and simplified case, it still constitutes an interesting problem since more advanced non-linear or time-dependent equations are treated in a very similar way, and since a uniform logically Cartesian mesh is often used in major parts of the domain. Since the most important operation in the solve phase is the application of the matrix-free operator, corresponding to a sparse matrix-vector product, we only consider this operation, rather than solving an actual problem.

In our experiments, we include a number of different versions of the stiffness operator. We have implemented these in a small C++/CUDA framework for matrix-free FEM computations. The implementations for the CPU use OpenMP for the parallelization, whereas the ones for the GPU use CUDA. We use double precision in all our computations, since high numerical accuracy is necessary for scientific applications.

#### Matrix-Free Versions

Six different matrix-free implementations of the stiffness operator are included; three for the CPU and three for the GPU, with the main difference being mainly how the conflicting updates are handled. Firstly, there is a serial version, Mfree, which simply performs all the elements on a single thread, in which case no protection from conflicting updates is needed. Secondly, the version Color utilizes the mesh coloring strategy described in Section 2.3.2, to process the elements in conflict-free chunks. Finally, there is a version PrivateBuffers which utilizes privatization in the same way as was used in the N-body experiments (see Section 3.3.4). By creating a separate result vector for each thread, they can safely perform their updates without risk for race conditions. Eventually, the multiple vectors are summed up in parallel in a reduction phase.

For the GPU, there is also one version, referred to as <code>GPU\_Color</code>, which uses mesh coloring. In the <code>GPU\_Atomic</code> version, we use atomic operations much like the compare-and-swap technique in the transactional-memory experiments (see Section 3.3). In CUDA, these are supported as intrinsic functions. At last, we include a third version <code>GPU\_Max</code> which processes the elements all at once much like the version using atomics, but performing the updates without any protection at all. This of course does not yield correct results, but is included as an reference of what performance to expect with perfect treatment of conflicts (i.e. no overhead). Due to the very large number of threads used by the GPU, the privatization approach used on the CPU is infeasible on the GPU.

#### **Matrix-Based Versions**